i/o缓冲器信息规范或称ibis,由于有效地满足了pcb设计师的分析验证需求而得到广泛认同。ibis标准随着缓冲器技术的日益进步而得到不断完善。但要适应当今高速缓冲器设计的复杂性要求,则需要从技术上开始考虑ibis与混合信号hdl及spice的配合使用。

一种新的缓冲器技术被研制出来后,其行为在ibis中得到标准化需要一段时间,取得现有的可用ibis仿真器对它的支持则需要更长时间。当前唯一可行的折衷方案是对该具体缓冲器施用spice电路表示法,但这样做的先决条件是ic供应商愿意提供其专有的设计信息。pcb设计师还须对许多部件加以集成。然而设计师现用的板级验证工具未必能做到对ibis和spice格式的同时支持。

一种有望得到迅速发展的高速缓冲器建模新方法是采用混合信号硬件描述语言对高级i/o特性进行原型模拟。ieee 1076.1是这样的语言之一,它也称作vhdl-ams。此语言在混合模拟/数字ic设计中得到了广泛使用,并受到eda供应商越来越多地青睐。就高速缓冲器建模应用而言,vhdl-ams结合了ibis的行为级建模能力与spice的无约束拓朴描述功能性于一身。

另外,可同时运行ibis、spice和vhdl-ams的新型多语言支持模拟技术已被开发出来,及时满足了高速pc板设计的需要。即使所用到的元件模型是一种多种格式的混合模型,该技术也支持完全的板级验证需求。

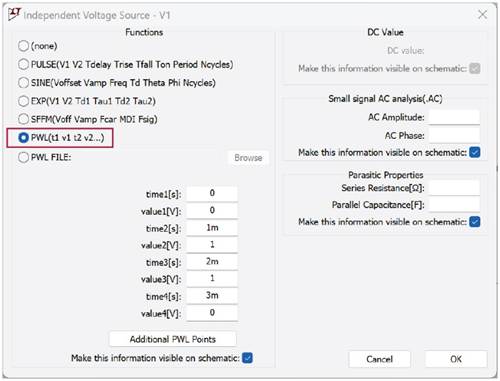

通过对一种具有'自适应端接'功能的高级输入缓冲器进行模拟来说明vhdl-ams的行为级建模能力。对该缓冲器建立的模型在结构上与ibis类似,包括箝位、元件电容量(c_comp)和逻辑阈值(vinl,vinh)。但模型中还包括一个带自适应电阻的输入端接,且此单元块对输入信号进行电压下冲检测。只要电压降到触发器阈值以下,它便以规定的量值减小内部电阻。这一过程一直沿续到传输线路(z0)达到良好的阻抗匹配为止。这种简单的点对点pcb网点连接在自适应过程中的电压波形和内部电阻值见右图。

hdl拥有强大的、富于弹性的行为级建模能力,它能适应未来几代缓冲器技术的发展需要。但在分析自动化方面仍需要提供附加信息。

ibis的另一个关键作用是规定哪些缓冲器与哪些引脚编号、各引脚的寄生效应、性能参数及标定数据相关联。如果板级验证模拟以自动方式进行,那么这些关键信息必须在缓冲器模型上有所反映。

基于这一原因,ibis必须继续充当为缓冲器模型提供上下整体关联的关键角色,而不只限于实际行为。mentor graphics公司目前正在与ibis未来工作组合作,共同界定ibis标准对外部模型调用的支持扩展。然后,将具有革新性的新型缓冲器行为以一种灵活的、可执行的形式(或为一个spice子电路或为一个hdl行为级模型)进行指定,与ibis传统提供的所有相关部件、封装和引脚信息集成。

hdl在高速pcb设计上的应用将为ic供应商带来无限的行为级建模能力。在系统设计层对分析和验证的同时支持,可带来缓冲器设计层的迅速进步和革新。最终这些都将转化为先进电子系统的更高性能、产量和更快的上市时间。