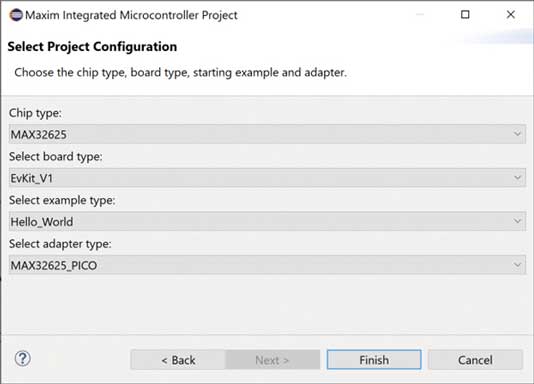

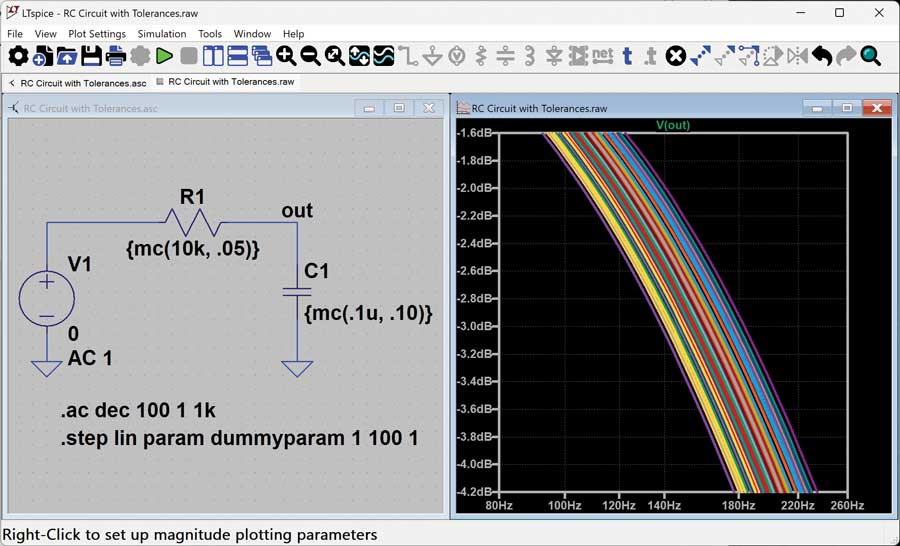

德州仪器|仪表 (ti) 宣布推出一款将 135 msps 的 16 位单通道模数转换器 (adc) 与低抖动时钟合成器进行了完美整合的信号链解决方案,从而可为通信、国防以及测量测试等高精度应用领域提供无与伦比的动态系统级性能。该数据转换器与时钟已集成在同一评估板(evm)上,有助于快速评估上述复杂系统。ads5483 adc 拥有高信噪比 (snr) 与无杂散动态范围 (sfdr),可通过第二尼奎斯特区 (nyquist zone) 接收来自 dc 的输入频率。采样速率为 135 msps 的 adc 在输入频率 (if) 为 70 mhz 时可实现 78.6 dbfs 的 snr 以及 95 dbc 的 sfdr,与同类 adc 相比,snr 高出 3.5 db,sfdr 高出 8 db。更高性能 ads 5483 能够显著增强设计灵活性,进而使众多应用受益匪浅。例如,其不仅可针对测量测试系统提供更高的准确度,而且还能凭借更高带宽在包括空中接口等在内的无线通信领域提供更高的灵敏度,如 wcdma、td-scdma、wimax、lte以及多载波 3 gsm 等。 在高带宽应用中,ads5483 通过集成全差动输入缓冲器(这也是 ti ads54xx adc 系列产品的通用特性)显著简化了模拟前端设计。该缓冲器采用 ti bicom3 高速工艺技术开发而成,可在整个输入频率范围内提供恒定输入阻抗,并能避免 adc 跟踪保持结构的反冲 (kickbac) 现象,以确保信号的持续线性 (consistent linearity)。此外,与同类adc竞争产品不同的是,ads5483 采用差分双倍数据速率 (ddr) lvds 输出,可显著减少其在 fpga 或 asic 器件上的 i/o 迹线数及引脚数。 超低抖动 cdce72010 时钟同步器能够提供低于 50 飞秒 (fs) 的最佳附加抖动性能,可充分满足 ads5483 等高速 adc 的时钟抖动需求。例如,配套提供的 evm 采用 cdce72010 与晶体带通滤波器以 122.8 msps 的速率驱动 ads5483,能够以 100 mhz 的输入频率实现极高的系统级 snr (78.0 dbfs snr) 与 sfdr (89.1 dbc)。 新型时钟同步器可支持各种频率,能够充分满足无线基站或测量测试设备等各类系统的要求。在频率高达 1.5 ghz,输入频率介于 8 khz~500 mhz 之间时,该同步器能够支持多达 10 个 lvpecl、10 个 lvds 或 20 个 lvcmos 可配置输出。此外,设计人员还能在同一时钟合成器中集成两组频率,并选择两个外接 vco/vcxo。cdce72010 的片上 eeprom 存储默认设置使设计人员能够缩短系统启动时间,并消除采用外接组件的麻烦。 ads5483 与 cdce72010 均在同一个 evm 上提供,有助于快速评估复杂系统。为帮助设计人员灵活地规则频率,该 evm 包含众多组件,如针对 vcxo 与晶振滤波器的开放式插槽以及针对外部源时钟输入的旁路功能。此外,ti 还可提供适用于其各种高速 lvds 输出 adc 系列的 tsw1200 数字采集五金|工具。tsw1200 可以快速评估高达 16 位分辨率以及 500 msps 采样率的 adc,从而不仅能够简化设计工艺,同时还可帮助设计人员加速相关系统的上市进程。 为进一步简化设计并加速产品上市进程,ti 推出了可形成完整信号链的种类繁多的各种器件.