This article looks at the different options for powering data acquisition in industrial automation applications using energy from the environment. It will focus on the energy sources most available in the industrial environment, from thermal energy to vibrational energy, and the design requirements for the data acquisition systems that use these low power sources.

It includes the V20W from Midé, thermal energy development kits from Cymbet and EnOcean and the BQ25504 power management IC from Texas Instruments, as well as the AD7988 ADC from Analog Devices as an example of how successive-approximation ADCs are used, and the AD7788 for sigma-delta devices.

Developments in data acquisition devices have pushed power consumption down to a level where it is now feasible to drive such devices from energy harvested from the environment. For industrial automation, this means vibrational and thermal energy can be used to power data capture from sensors, eliminating the need for power distribution infrastructure and allowing sensors to be placed in out-of-the-way places. This allows more systems to be measured, providing important data on the performance and health of equipment. This, in turn, allows equipment to be replaced before it fails, avoiding costly down time on the factory floor and providing significant cost savings to the operator.

There are several different architectures for data acquisition, and some are more suited to the combination of low power for energy harvesting sources and handling the input from sensors.

ADC architectures

While there may seem to be thousands of analog-to-digital converters (ADC) on the market, available through a search of the Digi-Key website, this can be confusing and overwhelming.

Most ADC applications come in four areas, from data acquisition and precision industrial measurement, to voiceband and audio applications with ‘high speed’ sampling rates greater than about 5 M samples/s (MSPS). These segments can all be served by successive-approximation (SAR), sigma-delta (∑Δ), and pipelined ADCs, but some are more suited to the needs of energy harvesting in industrial automation applications than others.

Successive-approximation

The successive-approximation ADC has been the workhorse of data acquisition since it was first used in experimental pulse-code-modulation (PCM) systems by Bell Labs in the 1940s. Modern devices have resolutions from 8 bits to 18 bits, with sampling rates up to several MHz. Output data is generally provided via a standard serial interface such as I²C or SPI, but some devices are available with parallel outputs. This requires more pins on the package and the board and consumes more power and so is not an option for energy harvesting systems.

In order to process rapidly changing signals, SAR ADCs have an input sample-and-hold (SHA) to keep the signal constant during the conversion cycle. The conversion starts with the internal D/A converter (DAC) set to midscale. The comparator determines whether the SHA output is greater or less than the DAC output, and the result (the most-significant bit (MSB) of the conversion) is stored in the successive-approximation register (SAR) as a 1 or a 0. The DAC is then set either to 1⁄4 scale or 3⁄4 scale (depending on the value of the MSB), and the comparator makes the decision for the second bit of the conversion. This result (1 or 0) is stored in the register, and the process continues until all of the bit values have been determined.

A key point is that the data corresponding to that specific sample is available at the end of the conversion time, with no pipeline delay or latency. This makes the SAR ADC easy to use in single-shot, burst-mode, and multiplexed applications. This works well for a sensor that may take a sample every few seconds, and an energy harvesting supply can use that spare time in the duty cycle to re-charge a battery from the local environment.

The internal conversion process of most modern IC SAR ADCs is controlled by a high-speed clock (internal or external, depending on the ADC) that does not need to be synchronized to the input.

Switched-capacitor (or charge-redistribution) DACs have become popular at the heart of today’s CMOS-based SAR ADCs. The principal advantage of the switched-capacitor DAC is that the accuracy and linearity are determined by small capacitors placed in parallel with the main capacitors. These are switched in and out under control of auto calibration routines to achieve high accuracy and linearity without the need for expensive thin-film laser trimming.

These switched-capacitor architectures also have good temperature tracking between the capacitors of around 1 ppm/°C, giving a high degree of temperature stability that is important for industrial environments.

Input multiplexing can be added to the basic SAR ADC function, allowing the integration of a complete data-acquisition system on a single chip. Additional digital functions, such as multiplexer sequencing and auto calibration circuitry, are also becoming common.

Figure 1: The basic successive-approximation architecture.

Sigma-Delta

Modern sigma-delta (∑Δ) ADCs have virtually replaced the integrating-type ADCs (dual-slope, triple-slope, quad-slope, etc.) for applications requiring high resolution (16 bits to 24 bits) and effective sampling rates up to a few hundred hertz. The higher resolution, together with on-chip programmable-gain amplifiers (PGAs), allows the small output voltages of sensors – such as weigh scales and thermocouples – to be digitized directly.

This also provides excellent rejection of 50 Hz and 60 Hz power-line frequencies with the right sampling rate and filter characteristics, a key advantage in industrial environments. ∑Δ ADCs offer an attractive alternative to traditional approaches using an instrumentation amplifier and a SAR ADC.

The basic concepts behind the ∑Δ architecture originated at Bell Labs in the 1950s in work done on experimental digital transmission systems using delta modulation and differential PCM. However, practical IC implementations did not appear until the late 1980s, when signal processing in digital CMOS became widely available. The basic concepts used in ∑Δ such as oversampling, noise shaping, digital filtering, and decimation are shown in Figure 2.

Figure 2: The basic first order ∑Δ modulator.

The heart of this basic modulator is a 1-bit ADC (comparator) and a 1-bit DAC (switch). Although there are a number of multi-bit ∑Δ ADCs, those using the single-bit modulator have an advantage of inherently excellent differential linearity.

The output of the modulator is a 1-bit stream of data. Because of negative feedback around the integrator, the average value of the signal at point B in Figure 2 must equal VIN. If VIN is zero (i.e., midscale), there are an equal number of 1s and 0s in the output data stream. As the input signal goes more positive, the number of 1s increases, and the number of 0s decreases. Likewise, as the input signal goes more negative, the number of 1s decreases, and the number of 0s increases. The ratio of the 1s in the output stream to the total number of samples in the same interval – the ones density – must therefore be proportional to the DC value of the input.

The modulator also accomplishes the noise-shaping function by acting as a low-pass filter for the signal and a high-pass filter for the quantization noise. The digital filter is an integral part of the ∑Δ ADC and can be optimized to give excellent 50 Hz/60 Hz power-frequency rejection. However, the digital filter does introduce inherent pipeline delay, which definitely must be considered in multiplexed and servo applications. If signals are multiplexed into a ∑Δ ADC, the digital filter must be allowed to settle to the new value before the output data is valid. Several output clock cycles are generally required for this settling. Because of the pipeline delay of the digital filter, the ∑Δ converter cannot be operated in a “single-shot” or “burst” mode.

Although the simple first-order single-bit ∑Δ ADC is inherently linear and monotonic because of the 1-bit ADC and 1-bit DAC, it does not provide sufficient noise shaping for high-resolution applications. Increasing the number of integrators in the modulator (similar to adding poles to a filter) provides more noise shaping at the expense of a more complex design.

Flash converter

A popular alternative to higher-order modulators is to use a multi-bit architecture, where the 1-bit ADC (comparator) is replaced with an N-bit flash converter, and the single-bit DAC (switch) is replaced with a highly linear N-bit DAC. Expensive laser trimming in multi-bit ∑Δ ADCs can be avoided by using techniques such as data scrambling to achieve the required linearity of the internal ADC and DAC.

The CMOS ∑Δ ADC is the dominant converter for today’s industrial measurement applications. These converters offer excellent power-line common-mode rejection and resolutions up to 24 bits, as well as digital conveniences such as on-chip calibration. Many have programmable-gain amplifiers (PGAs), which allow small signals from bridge and thermocouple transducers to be directly digitized without the need for additional external signal conditioning circuits and in-amps.

The ∑Δ ADC is an attractive alternative when very low-level signals must be digitized to high resolution. However, the ∑Δ ADC is more digitally intensive than the SAR ADC and may therefore require a somewhat longer development cycle, making it unsuitable for an energy harvesting power source. Evaluation boards and software can greatly assist in this process.

Energy harvesting with ADCs

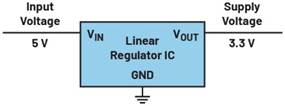

These devices can be powered from vibrational or thermal energy, usually with a power management device and an energy storage device such as a rechargeable battery or capacitor.

The specification of the data converter, particularly its power consumption and input voltage, has to map with the performance requirement of the application and the supply available from the energy harvesting source.

The CBC-EVAL-09 from Cymbet is a thermal energy generation evaluation board that provides a Peltier effect device to drive a data converter and a wireless link, integrating the DC-DC converter needed to provide the power. EnOcean’s EDK312C evaluation kit also uses thermal energy to power the data conversion and a wireless link.

The operation of these devices starts at typical 20 mV from a 2 Kelvin temperature difference at a standard low-cost Peltier element. The output power is in the range from μW to mW and depends on the actual temperature difference at the Peltier element. The ECT 310 in the development kit is designed and optimized for powering EnOcean radio modules for wireless sensors where the input voltage range of 20 mV to 50 mV corresponds to an output voltage range between 3 V to 4 V.

Figure 3: The Cymbet thermal energy harvesting evaluation kit.

Vibrational energy can be harvested using a piezoelectric sensor such as the Volture V20W from Midé. This is hermetically sealed for use in harsh environments and directly integrates with power management ICs and thin film batteries to provide reliable power for the data acquisition.

It is aimed specifically at powering data acquisition in industrial health monitoring networks, as well as wireless High Voltage Air Conditioning sensors in industrial automation settings. Being able to monitor the status of the HVAC is vital to ensure that the temperature on the factory floor is tightly controlled.

Figure 4: The Volture V20W piezoelectric vibrational energy generator from Midé.

The sensor is mounted on the vibration source and tuned to the resonant frequency of the source. Often the dominant frequencies are inherently known such as a 120 Hz AC motor or a 60 Hz appliance. However, most applications will require some form of vibration characterization.

The V20W then interfaces to power management devices such as the bq25504 from Texas Instruments. This is the first of a new family of intelligent, integrated energy harvesting, Nano-Power management solutions that are well suited for meeting the special needs of ultra-low-power applications.

The bq25504 is specifically designed to efficiently acquire and manage the microwatts (µW) to milliwatts (mW) of power generated from a variety of DC sources such as thermal electric generators. The bq25504 is the first device of its kind to implement a highly-efficient boost converter/charger targeted at wireless sensor networks (WSN) in industrial automation applications.

The design of the bq25504 starts with a DC-DC boost converter/charger that requires only microwatts of power to begin operating. Once started, the boost converter/charger can effectively extract power from low voltage output harvesters such as thermoelectric generators (TEGs) or single or dual cell solar panels. The boost converter can be started with an input voltage as low as 330mV, and once started, can continue to harvest energy down to VIN = 80 mV.

Figure 5: The Texas Instruments bq25504 power management controller for energy harvesting.

The bq25504 also implements a programmable maximum power point tracking sampling network to optimize the transfer of power into the device. Sampling the VIN_DC open circuit voltage is programmed using external resistors, and held with an external capacitor (CREF).

The bq25504 was designed with the flexibility to support a variety of energy storage elements. The availability of the sources from which harvesters extract their energy can often be sporadic or time varying. Systems will typically need some type of energy storage element, such as a rechargeable battery, super capacitor, or conventional capacitor. This storage element will make sure certain constant power is available when needed for the systems and also allows the system to handle any peak currents that cannot directly come from the input source.

To prevent damage to the storage element, both maximum and minimum voltages are monitored against the user programmed undervoltage (UV) and overvoltage (OV) levels. To further assist users in the strict management of their energy budgets, the bq25504 toggles the battery good flag to signal an attached microprocessor when the voltage on an energy storage battery or capacitor has dropped below a pre-set critical level. This should trigger the shedding of load currents to prevent the system from entering an undervoltage condition.

This combination of thermal or vibrational energy harvesting source, power management chip and storage device is then used to supply the energy for a low power ADC such as the AD7988-1 from Analog Devices. This is a fast, low power, single supply, precise 16-bit successive-approximation ADC with a 1.8 V supply that is suitable for energy harvesting applications. The AD7988-1 is capable of converting 100,000 samples per second (100 kSPS) and powers down between conversions. When operating at 10 kSPS, for example, the ADC consumes 70 µW typically, ideal for battery-backed EH applications.

Figure 6: A typical implementation using the AD7988 SAR ADC.

The AD7988 provides the user with on-chip track-and-hold and does not exhibit any pipeline delay or latency, making it ideal for multiple multiplexed channel applications. It can be interfaced to any 1.8 V to 5 V digital logic family. It is based on a charge-redistribution DAC. The capacitive DAC consists of two identical arrays of 16 binary weighted capacitors, which are connected to the two comparator inputs.

For sigma-delta designs, the AD7788 is a very low power, low noise, analog front-end device for low frequency measurement applications that are common in industrial automation applications. The converter uses a low noise, 16-bit, ∑Δ ADC with one differential input and operates from an internal clock and so does not need a separate clock, saving power. The 16.6 MHz output gives simultaneous 50 Hz/60 Hz rejection and operates from a single power supply from 2.5 V to 5.25 V, which can be supplied by the power management IC. When operating from a 3 V supply, these are particularly low power and suited to energy harvesting applications using a maximum of 225 μW. The device can be run in a single capture mode when it shuts down between each reading (or set of data captures) to conserve power, or with continuous capture.

Figure 7: The functional block diagram for the AD7788 16bit ∑Δ ADC.

Pipelined ADCs

While there is an overlap for ADCs for sampling rates between approximately 1 MSPS and 5 MSPS, above this rate is the territory of pipelined ADCs which are more often used in applications such as digital oscilloscopes, spectrum analyzers, and medical imaging as well as video, radar, and communications.

While these are fast, the pipeline delay, known as the latency, may be a problem if the ADC is in a feedback loop. It also makes pipelined ADCs difficult to use in multiplexed applications. Their performance at low sampling rates can also be an issue with energy harvesting designs in an automation setting if the sampling rate is reduced to meet the power budget. Because the internal timing generally is controlled by the external sampling clock, very low sampling rates extend the hold times for the internal track-and-holds to the point where excessive droop causes conversion errors. This means most pipelined ADCs have a specification for minimum as well as maximum sampling rate, and precludes operation in single-shot or burst-mode applications – where the SAR ADC architecture is more appropriate.

Conclusion

Successive-approximation is the architecture of choice for nearly all multiplexed data acquisition systems, especially powered from the local environment in an industrial automation application. It is relatively easy to use, has no pipeline delay, is available with resolutions to 18 bits and sampling rates up to 3 MSPS, and has a power budget consistent with an energy harvesting supply.

Sigma-delta ADCs are suitable for a wide variety of sensor-conditioning, energy-monitoring, and motor-control applications. In many cases, the high resolution and the addition of on-chip PGAs allow a direct connection between the sensor and the ADC without the need for an instrumentation amplifier or other conditioning circuitry. Low power versions with single capture capability are becoming available to support energy harvesting applications in industrial automation.

For sampling rates greater than 5 MSPS, the pipelined architecture dominates. These applications typically require resolutions up to 14 bits with high SFDR and SNR at sampling frequencies ranging from 5 MSPS to greater than 100 MSPS, but the power budget puts them out of the realm of most energy harvesting applications.