EDA技术是以大规模可编程逻辑器件为设计载体,以硬件语言为系统逻辑描述的主要方式,以计算机、大规模可编程逻辑器件的开发软件及实验开发系统为设计工具,通过有关的开发软件,自动完成用软件设计的电子系统到硬件系统的设计,最终形成集成电子系统或专用集成芯片的一门新技术。其设计的灵活性使得 EDA技术得以快速发展和广泛应用。本文以Max+PlusⅡ软件为设计平台,采用VHDL语言实现数字频率计的整体设计。

工作原理

众所周知,频率信号易于传输,抗干扰性强,可以获得较好的测量精度。因此,频率检测是电子测量领域最基本的测量之一。频率计的基本原理是用一个频率稳定度高的频率源作为基准时钟,对比测量其他信号的频率。通常情况下计算每秒内待测信号的脉冲个数,即闸门时间为1 s。闸门时间可以根据需要取值,大于或小于1 s都可以。闸门时间越长,得到的频率值就越准确,但闸门时间越长,则每测一次频率的间隔就越长。闸门时间越短,测得的频率值刷新就越快,但测得的频率精度就受影响。一般取1 s作为闸门时间。

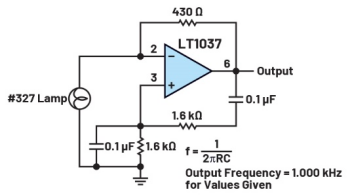

数字频率计的关键组成部分包括测频控制信号发生器、计数器、锁存器、译码驱动电路和显示电路,其原理框图如图1所示。

测频控制信号发生器

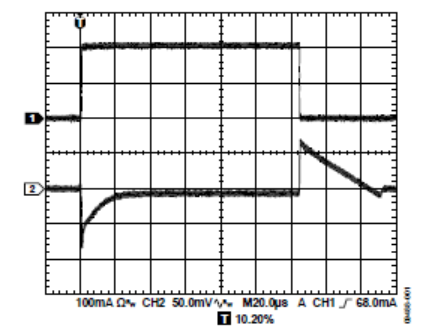

测频控制信号发生器产生测量频率的控制时序,是设计频率计的关键。这里控制信号CLK取为1 Hz,2分频后就是一个脉宽为1 s的时钟信号FZXH,用来作为计数闸门信号。当FZXH为高电平时开始计数;在FZXH的下降沿,产生一个锁存信号SCXH,锁存数据后,还要在下次 FZXH上升沿到来之前产生清零信号CLEAR,为下次计数做准备,CLEAR信号是上升沿有效。

计数器

计数器以待测信号FZXH作为时钟,在清零信号CLEAR到来时,异步清零;FZXH为高电平时开始计数。本文设计的计数器计数最大值是99 999 999。

锁存器

当锁存信号SCXH上升沿到来时,将计数器的计数值锁存,这样可由外部的七段译码器译码并在数码管上显示。设置锁存器的好处是显示的数据稳定,不会由于周期性的清零信号而不断闪烁。锁存器的位数应跟计数器完全一样,均是32位。

译码驱动电路

本文数码管采用动态显示方式,每一个时刻只能有一个数码管点亮。数码管的位选信号电路是74LS138芯片,其8个输出分别接到8个数码管的位选;3个输入分别接到EPF10K10LC84-4的I/O引脚。

数码管显示

本文采用8个共阴极数码管来显示待测频率的数值,其显示范围从O~99 999 999。

技术专区

- 聚焦IoT及车载电子 理光微电子深耕中国市场

- 泰科电子(TE Connectivity)亮相2018慕尼黑上海电子展 以创新科技连动

- 雷达没那么神秘就这点事!

- 基于树莓派的多串口多总线服务器设计

- 基于AD9371的经典小尺寸卫星通信解决方案