在实际的测试应用中,外围条件存在很多局限性,接触电阻、寄生电容和寄生电感无处不在,这些因素都会对测试造成影响。 本文将进行一次仿真实验,我们会从这个实验中了解在实际电流测试中电容和电感会对它产生什么影响,

做过测试的人都知道,当我们要测试电流的时候,如果在测试端加了电容,特别是较大的电容后,电流测试就变得不稳定,有可能测试值偏大,也有可能需要等到更长的时间才可能测试到稳定的电流值,这里面还不包含电容本身的漏电。

在这里,我们一起做一个仿真实验。

假设我们需要测试某个电阻的大小,我们采用加压测流的方式进行测试。我们假设这个电阻R1的大小为100K左右,我们施加在电阻两端的电压 V1=5V,通过测试通过R1(100K)的电流,我们就可以计算出对应的电阻来。如果是在比较理想的条件下,我们可以很容易就测试到50uA左右的电 流,然后通过计算得到100K的电阻。

然而,在实际的测试应用中,由于接触电阻、电感和电流的存在,都会对测试造成影响。

因为在实际测试中可以采用开尔文的方式进行测试,是可以消除接触电阻的影响的,所以,在这里,只考虑电容和电感的影响。

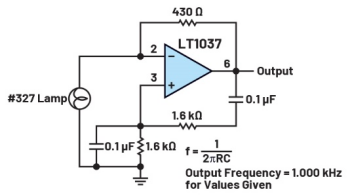

请大家看以下的仿真电路(采用了LTspice IV免费仿真软件,点击这里下载),我们需要测试通过R1的电流,而这个电流实际上是测试源V1本身测量到的。在实际条件下,测试源和需要测试的电阻之间,不可避免的存在寄生电感和寄生电容,我们分别定义为L1和C1。

我们可以预设一下L1=10nH,C1=10nF,我们假设V1从0V上升到5V的rising TIme为1mS。

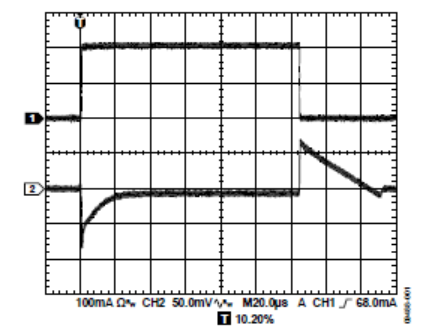

跑一下仿真,我们检测一下通过V1的电流(测试源测试到的电流),得到的仿真结果如下:

我们可以发现,电流的峰值达到了100uA左右(不考虑电流方向),而稳定后的电流值应该是50uA左右。为什么会有这个100uA的电流产生呢?这个,就是电容的影响。

根据电容的计算公式,我们可以得到i=C*dV/dt,根据已知条件,我们可以知道C=10nF,dV=5V, dt=1mS,通过计算,我们就可以得到i=100uA!如果电容C1计算增大到1uF呢,我们可以计算得到i=10mA!当然,实际的V1的 rising TIme会小一些,这个峰值电流也会小一些。但是,由于电容C1的存在,瞬间的峰值电流仍然可能很大!

特别是我们需要测试一些小电流的时候,我们往往需要使用较小的电流量程档来提高测量精度,但是,由于这个峰值电流的影响,有可能会使得测试源进入电流满量程或者电流钳位保护,无法进行测试;如果我们提高电流量程档,却又会对电流测量精度造成影响!

继续观察仿真图,我们还可以发现,电流在V1上升的瞬间就开始振荡,V1稳定以后(需要1mS时间),仍然在振荡,经过大约100uS以后才逐渐稳定下来。由于电流在振荡,我们必须等待足够的时间,待电流稳定以后再进行测试,否则,就可能造成电流测试的不稳定。

这是什么原因引起的呢,这是电感的影响!其实这就是一个LRC电路。L对振荡时间的影响是最大的。如果我们保持其它条件不变,取L1=100nH,振荡时间达到了2mS!而如果取L1=1nH, 振荡时间只有10uS左右了。

通过以上的仿真实验,我们了解了实际测试中电容和电感的影响,这就要求我们,设计合理的测试线路,减少外围器件的影响,同时也要尽量优化硬件设计,尽可能减少寄生电感和电容的影响。

技术专区

- smd封装是什么意思_smd封装有哪几种类型

- cob封装为何迟迟不能普及

- 一文看懂cob封装和smd封装区别

- Wavecrest双引擎技术实现信号完整性测试

- 利用逻辑分析仪和DSO解决信号完整性问题