ADC0804引脚图如下:

引脚功能及应用特性如下:

CS 、RD 、WR (引脚1、2、3):是数字控制输入端,满足标准TTL 逻辑电

平。其中CS 和WR 用来控制A/D 转换的启动信号。CS 、RD 用来读A/D 转换的结

果,当它们同时为低电平时,输出数据锁存器DB0~DB7 各端上出现8 位并行二进制数

码。

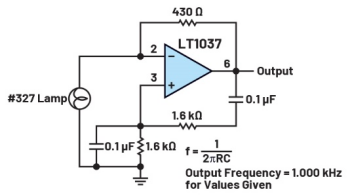

CLKI(引脚4)和CLKR(引脚19):ADC0801~0805 片内有时钟电路,只要在外

部“CLKI”和“CLKR”两端外接一对电阻电容即可产生A/D 转换所要求的时钟,其

振荡频率为fCLK≈1/1.1RC。其典型应用参数为:R=10KΩ,C=150PF,fCLK≈640KHZ,

转换速度为100μs。若采用外部时钟,则外部fCLK 可从CLKI 端送入,此时不接R、C。

允许的时钟频率范围为100KHZ~1460KHZ。

INTR (引脚5): INTR 是转换结束信号输出端,输出跳转为低电平表示本次

转换已经完成,可作为微处理器的中断或查询信号。如果将CS 和WR 端与INTR 端

相连,则ADC0804 就处于自动循环转换状态。

CS =0 时,允许进行A/D 转换。WR 由低跳高时A/D 转换开始,8 位逐次比较

需8×8=64 个时钟周期,再加上控制逻辑操作,一次转换需要66~73 个时钟周期。

在典型应用fCLK=640KHZ 时,转换时间约为103μs~114μs。当fCLK 超过640KHZ,转

换精度下降,超过极限值1460KHZ 时便不能正常工作。

VIN

(+)(引脚)和VIN

(-)(引脚7):被转换的电压信号从VIN

(+)和VIN

(-)输

入,允许此信号是差动的或不共地的电压信号。如果输入电压VIN的变化范围从0V

到Vmax,则芯片的VIN

(-)端接地,输入电压加到VIN

(+)引脚。由于该芯片允许差动

输入,在共模输入电压允许的情况下,输入电压范围可以从非零伏开始,即Vmin 至

Vmas。此时芯片的VIN

(-)端应该接入等于Vmin 的恒值电码坟上,而输入电压VIN仍然

加到VIN

(+)引脚上。

AGND(引脚8)和DGND(引脚10):A/D 转换器一般都有这两个引脚。模拟地

AGND 和数字地DGND 分别设置引入端,使数字电路的地电流不影响模拟信号回路,

以防止寄生耦合造成的干扰。

VREF/2(引脚9):参考电压VREF/2 可以由外部电路供给,从“VREF/2”端直接送

入,VREF/2 端电压值应是输入电压范围的二分之一。所以输入电压的范围可以通过

调整VREF/2 引脚处的电压加以改变,转换器的零点无需调整。

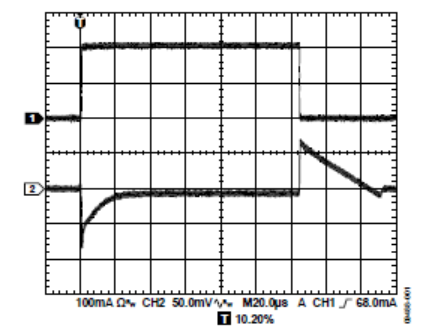

ADC0804 转换器的工作时序如图4-8 所示。

AD转换器的设计接口电路图:

图中,ADC0804 数据输出线与AT89C51 的数据总线直接相连,AT89C51 的RD 、

WR 和INT1直接连到ADC0804,由于用P1.0 线来产生片选信号,故无需外加

地址译码器。当AT89C51 向ADC0804 发WR (启动转换)、RD (读取结果)信号时,

只要虚拟一个系统不占用的数据存储器地址即可。