问题:

为什么使用DC-DC转换器应尽可能靠近负载的负载点(POL)电源?

答案:

效率和精度是两大优势,但实现POL转换需要特别注意稳压器设计。

接近电源。这是提高电源轨的电压精度、效率和动态响应的最佳方法之一。负载点转换器是一种电源DC-DC转换器,放置在尽可能靠近负载的位置,以接近电源。因POL转换器受益的应用包括高性能CPU、SoC和FPGA——它们对功率级的要求都越来越高。例如,在汽车应用中,高级驾驶员辅助系统(ADAS)——例如雷达、激光雷达和视觉系统——中使用的传感器数量在稳步倍增,导致需要更快的数据处理(更多功耗)以最小的延迟检测和跟踪周围的物体。

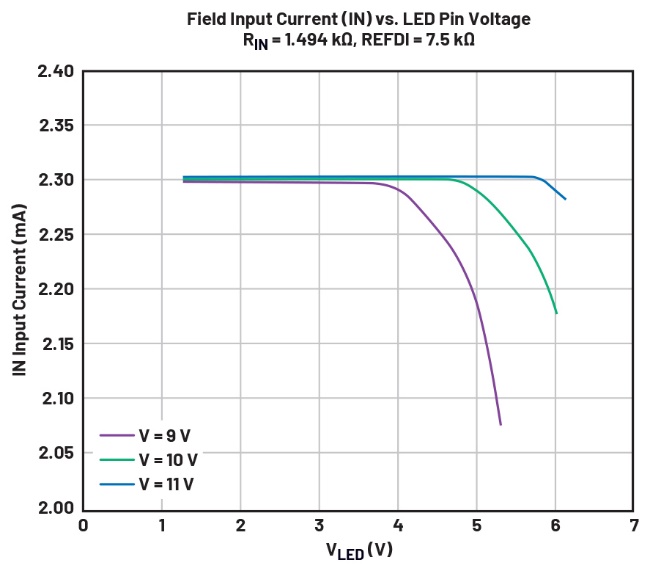

在这些数字系统中,有很多都使用高电流和低电压,因此更需要尽可能缩短电源和负载之间的距离。高电流导致的一个明显问题是,从转换器到负载,线路产生的电压会不断下降。图1和图2显示了电源和负载之间引线电阻的最小化如何使转换器的输出电压降最小化——本例中是控制器IC和为CPU供电的MOSFET。

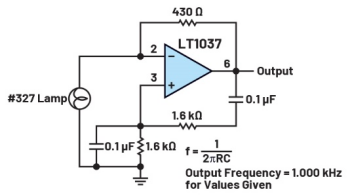

图2所示的较宽PCB走线减小了压降以达到精度要求,但还必须考虑寄生电感。图2中的PCB走线长度估计有约14.1 nh的电感,如图3的LTspice®模型所示。

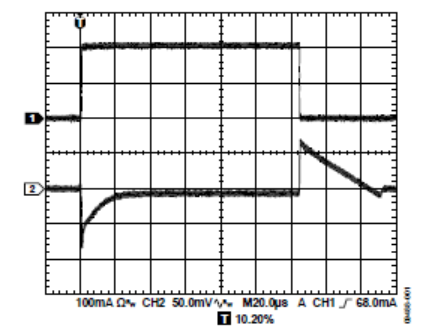

电感会抑制电流的动态变化di/dt,当负载变化时,经过该寄生电感的电流受其时间常数限制,瞬态响应劣化。寄生电感导致的结果是电压下降,如图4中的仿真图所示。