drc computer公司与其软件伙伴celoxica公司联合开发了用于关键算法加速的基于fpga的协处理器模块和软件开发工具。drc的这种协处理器模块基于赛灵思virtex-4 fpga系列,通过hypertransport总线与amd的opteron处理器连接。

drc公司首席执行官larry laurich表示,该技术初期主要瞄准石油和天然气、金融和生命科学应用,在这些领域,计算密集型算法可在fpga硬件中并行执行。首批开发系统会在今年第三季度面市,售价将为约2.5万美元。

在过去20年来,fpga吸引了产业界和学术界的广泛兴趣,一直被用作可配置计算平台。laurich透露,早在上世纪八十年代末,drc创办人steve casselman就对此产生浓厚兴趣,有意开发基于fpga的计算平台。casselman在1987年创办virtual computer公司,但该公司在2000年的低迷时期倒闭。

而随着规模更大、速度更快的fpga的问世,casselman成为率先认识到hypertransport总线有可能打破另一个瓶颈—相对低速的pci总线—的人士之一。casselman在2004年找到新的投资人,创办了drc公司,公司名“drc”即取“自动态可重配置协处理器”(dynamic reconfigurable coprocessor)之意。casselman现担任drc公司的首席科学家兼首席技术官。

laurich介绍,总部设在英国的celoxica公司是与drc签约的首个软件开发伙伴。他希望今后有更多的公司参与共同开发。

celoxica(美国)公司总经理jeff jussel表示,celoxica的工具提供了重新编译c代码以用于drc协处理器模块的能力。他说,fpga能并行运行许多算法,与传统服务器处理器相比,其功耗要低很多。

jussel表示:“举例来说,为了运行诸如black scholes这样的金融分析算法,银行会购买大量cpu和机架,其占用的空间越来越大,且需要大量能耗进行冷却。作为改进措施,银行可以采用fpga协处理器来分担其中一些关键算法,这样功耗要低很多的,同时性能表现却能提高100倍。”

jussel指出,相比过去一些用户通过开发asic来实现算法加速,如今这种基于fpga的方法要便宜很多,且为熟悉c语言编程工具的程序设计人员敞开了大门。

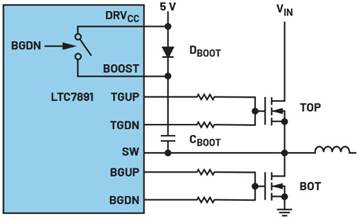

图2:drc的协处理器可实现计算算法加速。

laurich介绍,drc的协处理器模块与amd的opteron处理器管脚兼容,能插到ibm、惠普等大公司及其他十多家较小公司采用opteron处理器的主板上。hypertransport总线向opteron处理器传输数据的延迟时间约为60ns,这项指标仅是pci总线的大约1/10。此外,drc的协处理器模块可连接主板上的大量dram存储器。

“与那些dimm插槽通信的ddr控制器是我们知识产权(ip)的一部分。我们的ip使算法能以极低的延迟访问主板存储器。”laurich表示。一旦容量更大的ddr-2普及,drc的协处理器就有能力访问最高可达32gb的可用内存。

drc的协处理器模块由增加了几条指令的linux bios控制。该协处理器的标准配置是200mhz@8位,且可通过调整一个可协商(negotiated)接口来实现不同位宽度和位速率。

用户可期待该模块硬件能实现赛灵思承诺的性价比曲线。“我们已着手设计一款16位版本,预计在今年年中推出。眼下,该模块的最高速度为400mhz,但今后会变得更快,”laurich表示。现在,一个基于lx-60 virtex-4 fpga的模块,售价4,500美元,但他估计,明年将降为3,000美元。相关的开发系统包括一个带drc协处理器和opteron处理器的工作站、celoxica的工具,以及来自drc和赛灵思的软件。

laurich称,drc估计其技术能将整数应用程序加速约100倍、单精度浮点应用程序加速10倍,而双精度浮点应用程序运行速度可提高5倍。

作者:来大伟