摘要:给出了一种基于MC33591/MC33592设计的315MHz/434MHz OOK/FSK接收电路,该电路的数据速率为1~11kbaud,OOK/FSK灵敏度为-105dBm,最快唤醒时间为1ms,电源电压为:VGND-0.3~5.5V,在运行和配置模式时的电源电流为7.4mA,待机模式时的电流消耗为250μA,此外,该接收电路还具有三线SPI接口,可以直接与微控制器进行接口。

MC33591/MC33592是一个单片集成接收器,该芯片内含660kHz的中频带通滤波器、完整的VCO、可消除镜像的混频器、曼彻斯特编码时钟再生电路以及完整的SPI接口。可用于设计315MHz/434MHz OOK/FSK接收电路。

1 MC33591/ MC33592的引脚功能

MC33591采用LQFP24封装形式,其引脚排列如图1所示,各引脚功能如表1所列。

表1 MC33591/MC33592引脚功能描述

引 脚

符 号

描 述

1,2

VCC

5V电源

3

VCCLNA

5V LNA电源

4

RFIN

RF输入

5

GNDLNA

LNA接地端

6

GNDSUB

辅助接地端

7

PFD

连接到VCO控制电压

8

GNDVCO

VCO接地端

9

GND

芯片接地

10

XTAL1

基准晶振

11

XTAL2

基准晶振

12

CAGC

OKK IF AGC(自动增益控制)电容接入端,FSK基准

13

DMDAT

数据解频(OKK和FSK解调)

14

RESETB

状态机复位

15,16

MISO,MOSI

SPI输入/输出接口

17

SCLK

SPI接口时钟

18

VCCDIG

5V数学电源

19

GNDDIG

数字接地

20

RCBGAP

参考电压输出

21

STROBE

选通振荡器控制输入或待机/工作控制信号外部输入

22

CAFC

自动频率控制电容接入端

23

MIXOUT

混频输出

24

CMIXAGC

混频AGC(自动增益控制)电容端

2 内部结构与工作原理

MC33591/ MC33592的射频部分由能消除镜像干扰的混频器、660kHz的中频带通滤波器、自动增益控制级和OOK/FSK解调器组成。控制部分则包含有数据管理器、配置寄存器、串行接口、状态控制器等。其SPI接口可对调制方式进行编程选择。电路的数据可以从比较器输出,或者在数据管理器使能时从SPI端口输出。

2.1 本机振荡器

由于PLL环路滤波器已被集成在IC中,因此实际应用中的元器件数值可以根据本振参数在PFD引脚通过一个外部滤波器作略微的改进。使用者可以通过附加外部滤波器来选择最佳工作状况。锁相环电路增益可以由PG位编程设置,该位置为1时,环路为低增益状态。

2.2 通信协议

用MC33591/MC33592进行通信时,数据通过曼彻斯特编码后的占空系数:在OOK模式为48%~52%,而在 FSK模式时为45%~55%。此外,该通信协议编码还包括前同步(Preamble)、ID(识别)、报头(Header)字和数据等。其中ID(识别)字的内容是按曼彻斯特编码,并被预先装入电路中的配置寄存器2。识别字传输速率与数值传输速率一致。

为了与识别或报头字编码不同,前同步字的内容必须仔细定义。

报头字应当是4位曼彻斯特编码“0110”或者是它的补码。

一般数据(Data)应紧跟报头而没有任何延迟。数据由一个信息结束命令?End-of-Message EOM?结束,EOM由2个NRZ连续的1或0组成。当采用FSK调制时,数据由一个EOM结束,而不能简单地被射频信号终止。

图2给出了一个带有前同步字、识别字、报头字并跟随2数据位及结束字的完整信号,前同步通常放在识别和报头两个字的前面。

图3是一个使用ID检测的完整信号示意图。当接收机进入等待模式时,通常需要的设置时间一般为1ms。

2.3 数据管理器

数据管理器功能模块有五个用途,分别为ID(识别)字检测、 报头识别、时钟再生、SPI通道上的数据输出和时钟再生、信息结束检测。

2.4 串行接口

接收机(ROMEO2)和微控制器一般通过串行外部接口SPI(Serial Peripheral Interface)进行通信。如果不用SPI 接口,复位端POR ?Power On Reset?将设置接收机为默认结构来完成正确的操作。SPI接口通过以下三个输入/输出端来实现操作:

(1)串行时钟SCLK;

(2)主控输出受控输入MOSI;

(3)主控输入受控输出MISO。

主设时钟通过MOSI和MISO对数据输入/输出进行同步,主设备和从设备可在8个时钟周期内交换一个字节信息。操作时由主设备产生SCLK时钟并输入到从设备。MOSI在主设备中被配置为输入,而在从设备中则作为输出线;当主设备的MISI线配置为输出时,它在从设备中又作为输入线。

MISO和MOSI线一般向一个方向传输串行数据,并且最高位先发送。数据在SCLK的下降沿有效,在SCLK的上升沿移动。当没有数据输出时,SCLK和MOSI强制为低电平。使用Motorola的微控制器时,其时钟相位和极性控制位SPI必须设置为CPOL=0,CPHA=1。

2.5 配置寄存器

在配置模式中,只要在复位端(RESETB)保持一个长时间的低电平,微控制器将作为主设在SCLK上提供时钟信号,并在MOSI线上提供控制和配置位。如果不用默认配置,微控制器(MCU)将通过写入配置字到配置寄存器来改变配置。配置寄存器的内容可以返回到微控制器并进行检测。

当RESETB引脚为高电平时,如果数据管理器被使能(DME=1),接收机将作为主设在MOSI线上发送接收到的数据,同时在SCLK上发送接收到的时钟信号。

图3

当接收机SPI由主设(工作模式)变为从设(配置模式)或者由从设变为主设时,在模式转换前,MCU中的SPI推荐设置为从设。

在接通电源时,POR首先复位内部寄存器,以使接收机系统被设置在默认模式。在这个配置中,SPI是不使能的,同时接收机将在MOSI线上发送原始数据。实际上,默认配置可使电路作为一个没有外部控制的独立接收机来运行。

MC33591/MC33592有三个配置寄存器CR1~CR3。其中配置寄存器1(CR1)控制3个寄存器的存取(读或写),主要用于选择载波频率、设置数据调制方式、控制选通振荡器使能、定义选通比、控制数据管理器使能、定义报头字等。配置寄存器2(CR2)用于定义识别字的内容。配置寄存器3(CR3)则用于定义数据速率、设置混频器增益、控制MIXOUT引脚的转换、设置相位比较器增益等。

2.6 接收机的模式

通电复位后,接收机一般有三种不同的模式,第一种是睡眠模式,也就是低功耗模式。第二种是配置模式,用于对内部寄存器进行读写操作,在这种模式中,SPI处于从设位置并且接收机被使能。晶体振荡器振荡为SPI产生时钟信号。解调的数据可由DMDAT读出,但是不能通过SPI发送。第三种为工作模式,处于该模式时,接收机可以等待射频信号或接收信息。

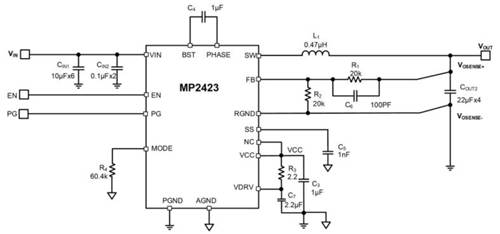

3 MC33591/592的应用电路

MC33591/MC33592的应用电路如图4所示。该电路在315MHz时应选择9.864375MHz晶振,而在434MHz时则应选13.580625MHz的晶振。采用FSK调制时,图4中的低通滤波电容C2的值与数据速率的关系如表2所列。

表2 采用FSK调制时C2与数据速率的关系

名 称

数据速率对应电容值

单 位

数据速率

1.2

2.4

4.8

9.6

kBaud

C2

100

47

22

12/10

nF