一、内存测试中的难点

内存广泛应用于各类电子产品中,内存测试也是产品测试中的热点和难点。内存测试中最为关键的测试项目为DQ/DQS/CLK之间的时序关系。JEDEC规范规定测量这几个信号之间的时序时测试点需要选择在靠近内存的最末端。而当前内存芯片大部分是BGA封装,有的甚至是正反贴的,这样有时候就很难在内存芯片的最末端找到测试点进行测试,如果在链路的中间位置进行测试,一方面信号会出现反射回沟等现象,从而影响到时序的测试,另外一方面对不同信号的测试点位置的不同,测量得到的时序就不是真实的时序结果。如下图1所示,探头无法点测到BGA封装的内存芯片的最末端管脚位置,此时准确的时序测量将会变得非常困难。

由于在信号链路的中间点进行的测试,因此信号波形将会因反射而出现明显的回沟,而且回沟正好出现在时钟信号上升沿和下降沿的中间位置,这会给时钟与数据之间的时序测量带来相当大的不稳定性,测量到的时序和实际情况也将会偏差很大。如下图2所示,测量到的时钟波形存在明显的单调性问题。

二、通过虚拟探测功能预测内存最末端的波形

力科示波器中的虚拟探测有如下两种方法:

1、使用EyeDoctorII软件的通道仿真功能

使用该方法需要设法获得测试点到链路末端的S参数,然后将S参数带入到示波器的EyeDoctorII眼图医生软件中(如图3所示界面)即可预测到末端信号的波形。但在实际应用中,由于测试点可能只是个过孔,测试点位于链路的中间,且也无法从测试点位置将链路断开成两部分,这样就很难测量得到测试点位置至链路最末端的S参数。如果通过软件从PCB板上进行S参数的提取会更加容易些,但是仿真的结果和实际情况还是会存在一定的差别。

2、使用力科示波器中的VP@Receiver虚拟探测功能

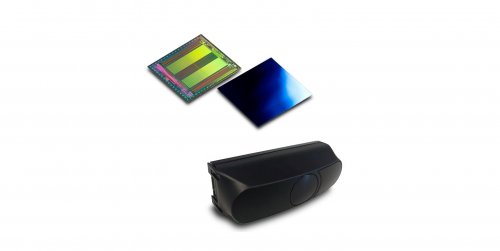

VP@Receiver的基本原理是先获得测试点到链路末端的传输线的延时Td、传输线末端的匹配模型(电容C,电感L,阻抗Z),然后将这些参数应用到实测到的波形上并推测出链路最末端的信号波形。下面以一个实例为例说明如何使用VP@Receiver来实现虚拟探测功能:

如下图5所示,我们能够通过示波器测量得到A点的信号波形,然后我们需要利用这个波形通过虚拟探测得到B点的波形。

为了获得这个波形,我们将测试点A点和链路末端B点之间的传输链路等效为上图5下方的电路模型。电路模型的主要参数包括链路传输延时T0,输入端电感Lin,输入端电容Cin,输入端阻抗RL。

技术专区

- 窄带物联网标准正式冻结,看NB-IoT数据传输测试

- ARM Powered 助你换一种方式打开世界,体验前所未有的新奇!

- VR--拓展虚拟视界,畅游梦幻与现实的未来

- 基于虚拟仪器技术的校准软件研制开发

- 宏达电继新款虚拟实境(VR)一体机之后,发表第2代HTC Vive Pro