为了追求以更低功耗和成本实现更高性能的目标,超大规模集成电路产业向系统级芯片(SoC)集成方向发展,从而导致了多时钟域设计的出现。最常见的是,当频率关系是2的整数倍时,共享相同时钟源的功能块具有同步交互性。从时序的角度看,这些交互可能经常发生在设计的关键路径。在这种情况下,你必须测试这些交互以查证过渡类型(transiTIon-type)故障,以达到测试覆盖率和DPPM(百万分之一缺陷)目标。

换句话说,在一个时钟域中具有发射触发器,并且在另一个同步时钟域中具有捕获触发器的路径被称为同步跨时钟域(SCCD)路径。如图1所示,FF1到FF2之间的组合云被称为内部时钟(intra-clock)域,而FF1到FF3之间的云被称为跨时钟(inter-clock)域。

图1:内部时钟域和跨时钟域路径可能会以延迟的形式引入故障。

用于过渡故障测试的时钟滤波电路(CFC)从时钟源滤除所需的时钟脉冲。典型的CFC具有局限性,不能用于测试跨同步时钟域的过渡故障。出现过渡错误时会出现什么问题?我们将解释这些限制,并建议对CFC进行改进、以使对SCCD的测试(如图1所示的跨时钟域故障)可行。

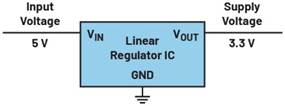

图2表示一个典型的时钟滤波电路,它有三个主要组件。

• 同步单元将扫描使能(SE)信号与工作时钟域同步。

• 由同步SE信号触发的可编程移位寄存器来控制集成时钟门控(ICG)以生成所需数量的时钟脉冲。

• ICG单元。

图2:典型的时钟滤波电路可能不足以测试跨同步时钟域的时钟故障。

全速故障测试包括两个步骤。第一步是移位模式,第二步是捕捉模式。在移位模式,当SE为高电平时,经由扫描链移位,寄存器被初始化为已知值。在捕捉模式,当SE为低时,功能路径的响应被捕捉到寄存器中。

在捕捉模式,CFC用于产生所需的时钟脉冲,用于全速测试的启动和捕捉周期。

当SE被选通,经过一段延迟才到达CFC。然后在CFC中,与接收时钟域的两级同步单元同步。被SE同步的信号将触发n级可编程寄存器给ICG提供使能信号,以滤除所需的时钟脉冲。这意味着来自CFC的时钟脉冲距离从SE到达CFC那一刻已有一定延迟。延迟主要由同步单元延迟造成。

图3:全速测试时钟的典型CFC输出波形。

为测试时钟域内的故障(内部时钟域故障),该CFC尽职尽责,如图3所示。但是,要测试SCCD过渡故障,需要产生启动和捕获脉冲,如图4所示。为获得这种波形,我们通常使用两个独立的CFC。每个时钟域都需要自己的CFC,因为每个时钟的脉冲宽度都不相同,因此需要从不同的CFC生成。图4给出了你可以实现的不同启动和捕获条件的示例。

图4:用于测试跨时钟域故障的典型启动和捕获脉冲组合,包括快速启动和慢速捕获以及慢速启动和快速捕获脉冲。

当用于测试同步复时钟域(图1)中的故障时,同一个CFC遇到以下挑战:

***边缘失齐***:当测试两个SCCD之间的故障时,每个时钟域都有自己的CFC。而由于CFC固有的同步延迟会导致输出错位。产生的时钟边缘将不会是周期对齐的。例如,假定频率为F和F/2的两个同步时钟,每个都具有移位寄存器长度为4的可编程CFC。可编程移位寄存器在不同时间被触发,从而导致CFC输出的不同延迟。假定为两级同步器,则时钟域F/2需要两倍于时钟域F的时间。图5显示了两个CFC的时钟输出波形。需要注意的是,有两种类型的错位失齐。一种是由于同步本身的延迟,如图5所示。

图5:通用CFC输出的时钟波形,显示失齐的边沿。

失齐的另一个原因是时钟偏斜(clock skew)。每个时钟的偏斜都导致两个CFC时钟输出失齐的进一步加剧。如图6所示,CFC_OUT_F的输出相对于CFC_OUT_F/2是偏斜的。正因为如此,捕获发射信号的功能时序窗口被压缩,损害了测试质量和有效性。

技术专区

- 抢占5G先机,下一代无线测试技术新挑战!

- 最全射频高速器件测试详细解读(图文)

- 如何通过电磁仿真模拟真实电磁波

- 联想小米OV计划三年20亿美金用于采购高通签署射频前端部件

- 示波器使用技巧,就应该这么用!