单片机里的DMA是什么

DMA就是直接存储器访问的首字母缩写(Direct Memory Access)。

CPU的总线上同时会挂着多几个存储器,如果想要将存储器1的内容复制到存储器2,如果不用DMA的话,就得靠CPU直接去操作了,操作过程大致是:CPU准备好存储器1的地址和控制信号,读取存储器1的内容,存放到CPU内部寄存器中,再准备好存储器2的地址和控制信号,将寄存器中的内容写入到存储器2。

如果是单个数据的操作,这个过程都是必须的,效率问题也不明显,但如果一次要复制大量数据(比如一帧图像数据、一批语音数据等),那么靠CPU这样循环一个数据一个数据地操作,不仅速度慢(由于架构设计的原因,一般CPU访问外部总线的速度都不是很高),还会导致CPU和总线一直被占用,效率就非常低了。如果在CPU内部做一个硬件控制器,专门负责这种数据搬移操作(自动产生存储器的地址和控制信号,自动实现读写时序),不仅速度可以提高很多,CPU还可以在此期间做其它的事情,这样效率就会高很多了。DMA就是这么个意思,硬件上必须有一个DMA控制器来实现这一功能。

现在DMA的概念和作用已经大大延伸了,很多复杂CPU里面甚至会包含很多个DMA控制器,DMA操作也不再仅限于外部存储器了,内部存储器之间、内部和外部存储器之间、各种标准外设和存储器之间,都有DMA控制器来实现数据交换,这样CPU的功能越来越强,数据处理也越来越快。

硬件介绍:

MSP430F15X/16X 系列单片机具有DMA 控制器,从而能够为数据高速传输提供保证。例如,通过DMA控制器可以直接将ADC 转换存贮器的内容传到RAM 单元。

MSP430系列单片机扩展的DMA具有来之所有外设的触发器,不需要CPU的干预即可提供先进的可配置的数据传输能力,从而加速了基于MCU的信号处理进程,DMA传输的触发来源对CPU 来说是完全透明的,DMA控制器可在内存与外部及外部硬件之间进行精确的传输控制。DMA 消除了数据传输延迟时间以及各种开销,从而可以解放16为RISC CPU,以便其将更多的时间用于处理数据,而非执行正在处理的任务。

MSP430F16x系列单片机的DMA模块有以下特点:数据传送不需要CPU介入,完全由DMA控制器自行管理。在整个地址空间范围内传输数据,块方式传输可达65536字节;能够提高片内外设数据吞吐能力,实现高速传输,每个字或者字节的传输仅需要2个MCLK;减少系统功耗,即使在片内外设进行数据输入或输出时,CPU也可以处于超低功耗模式而不需唤醒;字节和字数据可以混合传送:DMA传输可以是字节到字节、字到字、字节到字或者字到字节。当字到字节传输时,只有字中较低字节能够传输,当从字节到字传输时,传输到字的低字节,高字节被自动清零;四种传输寻址模式:固定地址到固定地址、固定地址到块地址、块地址到固定地址以及块地址到块地址;触发方式灵活:边沿或者电平触发。单个、块或突发块传输模式:每次触发DMA操作,可以根据需要传输不同规模的数据

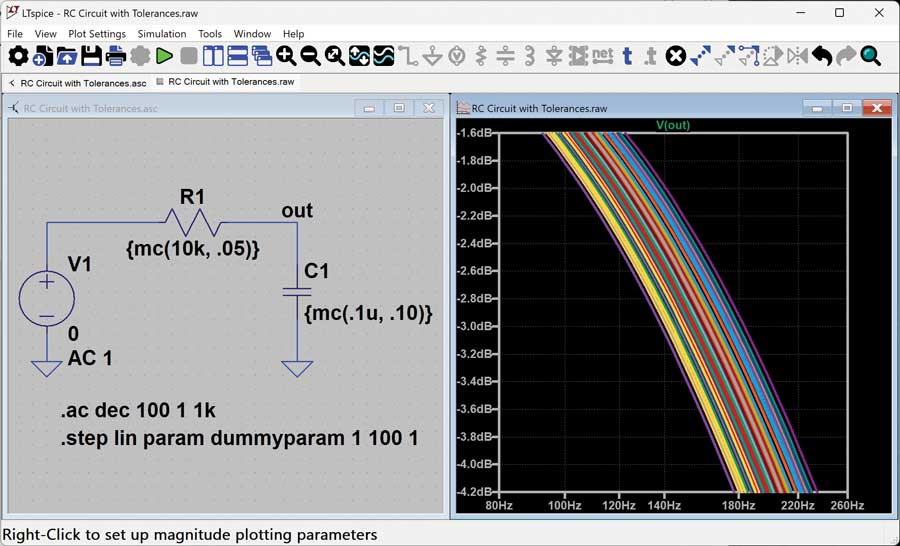

DMA的四种寻址模式如下图所示:

DMA控制器模块:3个独立的传输通道:通道0、通道1和通道2。每个通道都有源地址寄存器、目的地址寄存器、传送数据长度寄存器和控制寄存器。每个通道的触发请求可以分别允许和禁止;可配置的通道优先权:优先权裁决模块,传输通道的优先级可以调整,对同时有触发请求的通道进行优先级裁决,确定哪个通道的优先级最高。MSP430的DMA控制器可以采用固定优先级,还可以采用循环优先级。程序命令控制模块,每个DMA通道开始传输之前,CPU要编程给定相关的命令和模式控制,以决定DMA通道传输的类型;可配置的传送触发器:触发源选择模块,DMAREQ(软件触发)、TImer_ACCR2输出、TImer_BCCR2输出、I2C 数据接收准备好、I2C 数据发送准备好、USART接收发送数据、DAC12模块DAC12IFG、ADC12模块的ADC12IFGx、DMAxIFG、DMAE0 外部触发源。并且还具有触发源扩充能力。

DMA有六种传输模式:单字或者单字节传输;块传输;突发块传输;重复单字或者单字节传输;重复块传输;重复突发块传输。前三个,传输完成后DMAEN自动复位;再次传输时需要重新置位DMAEN位以使能DMA通道。后三个为重复模式,一次传输完成后,DMAEN不复位;再次出发时,可以再次启动数据传输。六种传输模式通过DMADTx寄存器设置:

DMADTx Transfer Mode DescripTIon

000 Single transfer Each transfer requires a trigger. DMAEN is

automaTIcally cleared when DMAxSZ transfers have

been made.

001 Block transfer A complete block is transferred with one trigger.

DMAEN is automatically cleared at the end of the

block transfer.

010, 011 Burst-block transfer CPU activity is interleaved with a block transfer.

DMAEN is automatically cleared at the end of the

burst-block transfer.

100 Repeated single transfer Each transfer requires a trigger. DMAEN remains

enabled.

101 Repeated block transfer A complete block is transferred with one trigger.

DMAEN remains enabled.

110, 111 Repeated burst-block CPU activity is interleaved with a block transfer.

transfer DMAEN remains enabled.

单字或者单字节传输:DMA 通道被定义为单字或者单字节传输模式,每个字或者字节的传输都要触发信号触发。设置DMADTx=0 就定义了单字或者单字节传输模式,规定的传输完毕后DMAEN 位自动清除,如果需要再次传输,必须重新置位DMAEN。如果设置DMADTx=4 为重复单字或者单字节传输模式,DMAEN 位一直保持置位,每次触发伴随一次传输。DMAxSZ 寄存器保存传输的单元个数,如果该寄存器为0,则没有传输。传输之前DMAxSZ 寄存器的值写入到一个临时的寄存器中,每次操作之后DMAxSZ 做减操作。当DMAxSZ减为零的时候,它所对应的临时寄存器将原来的值重新置入DMAxSZ,同时相应的DMAIFG标志置位。

块传输模式:在块传输模式,每次触发可以传输一个数据块。设置DMADTx=1 为块传输模式,每个数据块传输完毕,DMAEN 位自动清除,在触发传输下一个数据块之前,该位要被重新置位。在传输某个数据块期间,其他的传输请求将被忽略。设置DMADTx=5 为重复块传输模式,某个数据块传输完毕,DMAEN 位仍然保持置位,之后,新的触发可以引起又一次数据块传送。DMAxSZ 寄存器保存数据块所包含的单元个数。DMASRCINCR 和DMADSTINCR 反映在数据块传输过程中的目的地址和源地址的变化情况。在块传输或者重复块传输过程中,DMAxSA,DMAxDA,DMAxSZ 寄存器的值写入到对应的临时寄存器中,DMAxSA,DMAxDA寄存器所对应的临时值在块传输过程中增加或者减少,而DMAxSZ 在块传输过程中减计数,始终反映当前数据块还有多少单元没有传输完毕,当DMAxSZ 减为0,它所对应的临时寄存器将原来的值重新置入DMAxSZ,同时相应的DMAIFG被置位。在块传输过程中,CPU 暂停工作,不参与数据的传输。数据块需要2×MCLK×DMAxSZ 个时钟周期。当每个数据块传输完毕,CPU 按照暂停前的状态重新开始执行。

突发块传输模式:这个和块传输模式类似,只不过每传输4个字或字节,DMA释放内部总线,CPU运行2个MCLK周期;在传输过程中CPU有20%的执行时间,而块传输需要等DMA完全传送完之后,CPU方能运行。

DMA触发源:每个通道的触发源有DMAxTSELx位进行控制的,这些位必须在DMAEN位为0是进行设置,否则可能出现不可预料的DMA触发。

DMAxTSELx Operation

0000 DMAREQ bit (software trigger)

0001 TACCR2 CCIFG bit

0010 TBCCR2 CCIFG bit

0011 URXIFG0 (UART/SPI mode), USART0 data received (I2C mode)

0100 UTXIFG0 (UART/SPI mode), USART0 transmit ready (I2C mode)

0101 DAC12_0CTL DAC12IFG bit

0110 ADC12 ADC12IFGx bit

0111 TACCR0 CCIFG bit

1000 TBCCR0 CCIFG bit

1001 URXIFG1 bit

1010 UTXIFG1 bit

1011 Multiplier ready

1100 No action

1101 No action

1110 DMA0IFG bit triggers DMA channel 1

DMA1IFG bit triggers DMA channel 2

DMA2IFG bit triggers DMA channel 0

1111 External trigger DMAE0

另外,单片机的中断程序不影响DMA的传输,当DMA传输过程中,单片机不响应中外部NMI中断(必须DMA的控制位ENNMI位为1时响应NMI中断,否则不予处理)外的所有中断;必须等待DMA数据传送结束之后才运行系统的中断处理程序。

DMA的中断:数据传送过程中,DMAxSZ寄存器值减为0时,DMA置位DMAIFG,DMA的中断和DAC12模块共享中断向量,使用中断时需要软件判断具体是那个中断。中断响应后DMAIFG不会自动复位,使用时必须软件清零DMAIFG位。

DMA的寄存器如下:

Register Short Form Register Type Address Initial State

DMA control 0 DMACTL0 Read/write 0122h Reset with POR

DMA control 1 DMACTL1 Read/write 0124h Reset with POR

DMA channel 0 control DMA0CTL Read/write 01E0h Reset with POR

DMA channel 0 source address DMA0SA Read/write 01E2h Unchanged

DMA channel 0 destination address DMA0DA Read/write 01E4h Unchanged

DMA channel 0 transfer size DMA0SZ Read/write 01E6h Unchanged

DMA channel 1 control DMA1CTL Read/write 01E8h Reset with POR

DMA channel 1 source address DMA1SA Read/write 01EAh Unchanged

DMA channel 1 destination address DMA1DA Read/write 01ECh Unchanged

DMA channel 1 transfer size DMA1SZ Read/write 01EEh Unchanged

DMA channel 2 control DMA2CTL Read/write 01F0h Reset with POR

DMA channel 2 source address DMA2SA Read/write 01F2h Unchanged

DMA channel 2 destination address DMA2DA Read/write 01F4h Unchanged

DMA channel 2 transfer size DMA2SZ Read/write 01F6h Unchanged

有关每个寄存器的详细内容参考ti提供的用户指南。

技术专区

- Alexa语音服务软件扩展STM32Cube

- 结合DNN API驱动未来神经网络应用的解决方案

- 针对于高端移动通信和汽车市场的四集群设计

- 一款基于帧捕捉的开源图形调试器应用设计

- 即将成为标准配置的最新安全技术:后视摄像系统