在近日举行的intel一年一度research@intelday007活动上,除了再次展示terascale80核每秒两万亿次运算的惊人能力外,intel开发人员还透露了对此概念处理器的下一步研发计划,即引入半导体堆叠封装技术。

intel准备在terascale处理器的下一代产品中,一改目前处理器核心与缓存在同一平面上的传统做法,将sram缓存叠放在运算核心的顶部。这样做可以将运算核心与缓存间的带宽最大化,同时降低芯片的封装面积,有利于进一步提高频率。

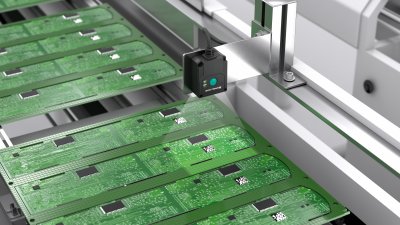

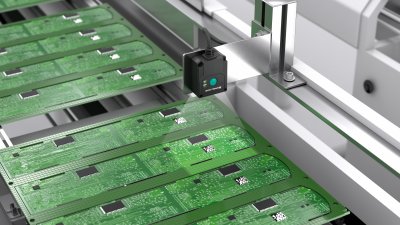

intel展示了terascale处理器晶圆。图中标号一的部分是80个处理器核心,而标号2则是缓存部分。它们在同一块晶圆上制造,与传统处理器制造的区别在于,封装阶段,它们不再像图中这样平行放置,而是进行叠放。