作者:罗翠钦

在半导体应用广泛的3c产品中,以手机、pda为代表的数字消费产品(digital consuner)的发展反映出半导体产业发展的趋势:上市时间越来越短,成本要求不断降低,同时多种功能的集成使soc复杂度增加。因此,cadence亚太区总裁居龙把“在最短时间,开发出最低成本、最复杂的产品”,称为整个半导体产业面临的共同故事。

商业挑战面前,半导体产业的技术挑战也愈加棘手。随着集成电路工艺在从微米时代步入纳米时代,如今要经历从90nm、65nm、45nm、32nm的工艺提升,同时物理现象也发生变化,不同的工艺带来不同的设计挑战。现在,最重要的挑战是低功耗。漏电流是65nm面对的第一大问题,物理现象改变了,设计方法和工具也要改变。此外,良率、可靠性、高集成度都是技术方面的挑战。

从概念到产品推向市场,eda服务于产业链整合

半导体产业发展到今天,eda作为ic设计不可或缺的支撑工具,要在“最短时间、开发出最低成本、最复杂的产品”,仅仅提供“点”工具是不够的。

因此,居龙指出:“当今,整个设计链(包括设计、制造、封装)分工越来越细,fabless远远多于idm(集成器件制造商),单个公司无法面对所有的工作,公司成功与否取决于产业链整合是否高效。从概念到市场,eda工具要服务于产业链的整合,包括从系统级设计、物理实现、封装设计、加工制造、pcb设计整个过程,都需要eda工具的辅助支持。”

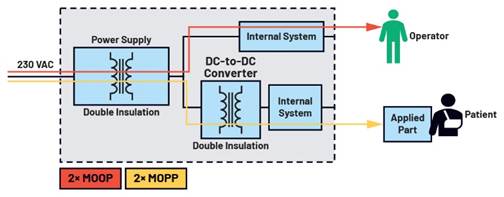

从概念到产品推向市场,整个电子设计分为几块:ic设计->封装设计->ic制造->pcb设计。“整个设计周期大概需要半年到一年时间,一个产品才可以推向市场。在ic制造、pcb设计环节等环节都存在一些技术设计挑战,会影响到产品上市时间、良率。”该公司资深设计服务专家赖志广讲解了eda的角色,“在整个设计流程中eda都守候在一旁,提供一个辅助平台,对所有产品设计流程中提供强有力的帮助。”

cadence的技术平台分为5个不同的产品线,全面的设计工具可以提供从概念到产品实现最完整的解决方案。包括针对大规模、复杂、高性能的数字ic设计平台encounter;用于模拟、混合信号、rf集成电路设计的全定制设计平台virtuoso;支持最快、最有效大规模复杂芯片验证的功能验证平台incisive;面向目标、按时完成系统协同设计的系统互联设计平台allegro,以及在生产加工前进行可信赖加工验证的可制造性设计技术。

垂直解决方案(或称“锦囊”)是cadence为帮助ic设计公司迅速建立设计架构,并获得更短、可预测性更高的设计周期而推出的,独具特色的整套解决方案。“锦囊”通过与一个打包在平台流程中经过验证的方法学、授权标准ip相结合,用于解决特定的应用设计问题。当前,cadence的“锦囊”重点在无线领域,以及有线网络、个人娱乐领域,已有5个方案(包括rf sip methodology kit、functional verification kit for arm、ams methodology kit、optimization methodology kit for arm processors、rf design methodology kit)。

“cadence有最完整的解决方案,能够为客户提供全面的增值,这是我们的优势。”居龙也进一步解释了小公司难成气候,“今后几年大公司就变成大者恒大,小公司生存空间非常小,顶多做出一个不错的技术卖给大公司,不可能再会上市。”

系统功能验证、可制造性设计是未来成长空间

传统eda市场主要集中在rtl和gds。如今,在eda市场增长遭遇瓶颈的大环境下,业界都在探寻eda新的成长空间。

居龙谈到cadence要把握两个新的成长空间,这也是cadence看到的客户需求。

一方面,芯片和系统的结合越来越紧密,要把系统所有功能放到芯片上去,将面临系统功能验证的挑战,因而cadence现在一个新的产品方向是提供系统功能验证的解决方案,使产品从规格设计到实现能很快实现。

另一方面是制造,ic设计完成后,但是否以很好的成本生产出来,以及跟fountry的结合是否够密切,可制造性设计(dfm)也是未来发展方向。cadence和pdf solutions已就dfm架构蓝图开发开始合作。

在中国市场,cadence也正在与信息产业部就合作事宜进行积极磋商。谈到cadence与中国政府在ip合作上的考虑,居龙称:“cadence希望与政府合作不是要卖ip,而是通过与政府政策带动整个产业。我们的想法是:自己不卖ip,而是希望把国外ip带进来,国外ip公司要进入中国,一方面他们担心自己ip被侵权,另一方面怎样帮助他们把ip真正利用起来,像mips、arm吸引很多支持,能不能及如何进行验证、集成。”他强调,ip不是独立的,只有设计出真正的产品它才有价值,而像intel真正有价值的ip也是不卖的。