石英晶体在外加电压的作用下,它会产生一个压电效应,石英晶体产生机械振动,当外加电压的频率与晶体固有振荡频率相同时,晶体的机械振幅最大,产生的交变电场也就最大,形成压电谐振。

从石英晶体的电抗频率特性可知,它有两个相当接近的谐振频率,一个串联谐振频率,一个并联谐振频率,当石英晶体处于串联谐振时电抗最小,当处于并联谐振时电抗最大,当处于这两个频率范围之间时,石英晶体呈电感性,当游离这两个频率之外时,石英晶体呈容性。

screen.width-333)this.width=screen.width-333" border=0 dypop="按此在新窗口浏览图片">

此主题相关图片如下:

screen.width-333)this.width=screen.width-333" border=0>

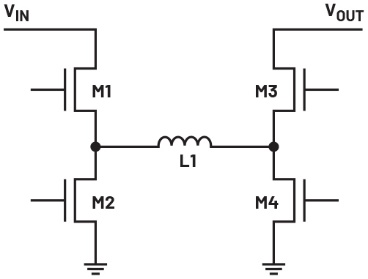

图a是工作于串联谐振状态的ttl门电路振荡器(摘protel99se附带例),当电路频率为串联谐振频率时,晶体的等效电抗接近零(发生串联谐振),串联谐振频率信号最容易通过n1、n2闭环回路,这个频率信号通过两级反相后形成反馈振荡,晶体同时也担任着选频作用。也就是说在工作于串联谐振状态的振荡电路,它的频率取决于晶体本身具有的频率参数。

此主题相关图片如下:

图b是工作于并联谐振状态的cmos门电路振荡器,晶体等效一个电感(晶体工作于串联谐振频率与并联谐振频率之间时,晶体呈电感性)与外接的电容构成三点式lc振荡器,通过外接的电容可对频率进行微调。

电阻r接在反相器n3的输入与输出端,其目的是将n3偏置在线性放大区,构成放大器。

从晶体x的两端看c1、c2(图b),它们是通过gnd串联成一个电容(这个串联电容(cx)可以由公式《cx=c1c2/c1+c2》求出),x与串联电容构成一个并联共振电路(为了方便,我这里只简单的将晶体等效为电感性),从电容一分为二的电路形态上看,晶体和电容c1、c2也是构成一个π型选频网络反馈通道(也称π型谐振电路)。

n3放大器的输出端信号通过x、c2、c1构成的π型谐振电路返回n3放大器的输入端,形成反馈振荡,由此可见它的振荡频率是由π型谐振电路所决定的(当然,主要还是晶体所决定)。

也是由于n3的输出端连接着x、c1、c2π型谐振电路,而且输出信号近似于正弦波,为防止负载电路对振荡电路的干扰和提高带载能力,n3的输出信号需通过n4的缓冲、放大整形后再接到负载。

在晶体x与串联电容cx构成的并联共振电路里,cx的损耗电阻大时,电路的q值必然下降,同时会使晶体的特性恶化,引起cx这个损耗电阻增大的因素是来自多方面的,但电阻r起到较大的作用,通常在提供足够激励的情况下,尽可能增大r的电阻值或在n3输出端与选频网络间(即bc间)串入一个电阻,从c2看阻抗也加大,一般电阻r的取值为1m~30m。

另,在c1、c2之间的连接也要引起注意,连接线粗而短,不单可以减少产生损耗,而且还能防止混入干扰源而干扰了振荡器的正常工作。

晶体外壳所标注的频率,既不是串联谐振频率也不是并联谐振频率,而是在外接负载电容时测定的频率,数值界乎于串联谐振频率与并联谐振频率之间。

这也就是说,即使两个晶体外壳所标注频率一样的晶体,其频率也会有些少偏差(工艺引起的离散性),我们在应用晶体时,负载电容(cx)的值是直接由厂家所提供的,我们无需再去计算。

在要求不高的实际应用中,我们为了设计方便,一般可以将负载电容cx分压值分拆为1:1,即c1=c2(公式见上),在要求较高的情况下,这样的方便显然是不合理的,首先,c1应减去门电路的输入平均电容和各项因素产生的离散电容(估算),同理,c2也应减去各项因素产生的离散电容(估算),然而,由于元件的离散性和估算存在着偏差,频率依然不是很准确,我们可适当减小c1或c2的值再并个微调电容加以调整(通常是c1)。

要得到较精确的频率,电容除了需选用损耗小、特性好的产品外,pcb布板和各元件温度系数的选取也很重要。