设计了基于CPLD的数字电压表,采用CPLD器件作为核心处理电路,用单片机进行控制,能较好地减小外界干扰,提高分辨率。该数字电压表能够自动转换量程,从而可提高数字电压表的性能。

1 方案论证与比较

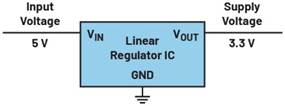

双积分A/D是对输入取样电压和基准电压进行两次积分,以获得与取样电压平均值成正比的时间间隔,同时在此时间间隔内,用计数器对CP记数,计数器的输出结果就是对应的数字量。双积分A/D有精度高,抗干扰能力强和稳定性好的优点,但转换速度较低,因而适用于数字直流电压表等精度较高而转换速度要求不高的仪器。设计的系统框图如图1所示。为实现该系统功能,可采用以下两种方案。

1.1 方案一

用J-K触发器构成n位二进制异步加法计数器,并采用下降沿触发器FF。但因J-K触发器数目与显示精度有关,若显示精度较高,则所需触发器数目较多,需占大量空间,且易受干扰。若2 V档的最小分辨率为0.1 mV,则有2/(2n-1)=O.1 mV,n≥15,这里取n=16,如图2所示。

1.2 方案二

采用EDA可编程逻辑器件把16位J-K触发器组成的计数器和控制电路集成到系统内部,不仅可以消除外界干扰,减小测量误差,且大大节省空间,提高系统的响应速度。CPLD使用方便、快捷,性价比很高,如图3所示。

对比两种方案的性能,本设计选用方案二。

2 系统设计

2.1 硬件部分

2.1.1 滤波电路

滤波电路采用压控二阶低通滤波器,如图4所示。运放采用低温漂高精度运放OP07,取R1=R2=R=1.592 kΩ,C1=C2=10μF,则f0=10 Hz。

传递函数为:

当Aup《3时,电路才能正常工作,不产生自激振荡。令:

![]()

则电压放大倍数:

![]()

对直流信号的放大倍数为:

![]()

2.1.2 测量放大器

测量放大器如图5所示。AD620为低功耗高精度仪表放大器,其增益为:

![]()

即可通过调节引脚1,8间电阻的大小来调节G。

对于不同大小的信号,单片机通过8选1模拟开关CD4051来选择电阻R1,R2,R3,R4的接入,实现不同增益值。将0.1 mV~2 V分为4个量程,即0.1~2 mV,2 mV~20 mV,20~200 mV,200 mV~2 V,分别放大1 000,100,10,1.1倍,则可选R1=49.45 Ω,R2=499 Ω,R3= 5.489 kΩ,R4=494 kΩ。

2.1.3 双积分转换电路

双积分转换电路如图3所示。

(1)积分器:由R,C和运放组成,分别对输入电压和基准电压进行积分,其输入接AD620输出。

(2)检零比较器:运放反相端接积分器的输出UA;运放同相端接地。当UA

(3)可编程逻辑器件:EPM7128是CPLDMAX7000S系列器件,内部带有存储器,不需要外接。内部为门控开关、16位计数器、16位数据寄存器和辅助触发器。门控开关控制计数器开始计数;计数器用来对CP脉冲进行计数,并触发辅助触发器;寄存器寄存计数器数值,等待单片机读取;辅助触发器通过控制S1来控制对取样电压和基准电压的积分。单片机通过Vs对CPLD进行控制。

第1次积分取样时,Qc=O,控制S1掷向输入电压Vi,L=0,控制S2断开,电容放电。积分输出电压为:

2.1.4 显示模块

用CAl602A液晶模块显示所测电压值。CAl602A字符型液晶是用5&TImes;7点阵图形来显示字符的液晶显示器,它微功耗、体积小、带译码和驱动电路使用方便、人机界面也很直观,如图6所示。

2.2 软件部分

2.2.1 软件流程图

(1)主程序如图7所示。

(2)子程序包含量程转换(见图8),数据采集(见图9),自动校准(见图10),液晶显示(见图11)4个子程序。

量程转换:

BC=01时,1~20 mV档,放大100倍;

BC=10时,20~200 mV档,放大10倍;

BC=11时,200 mV~2 V档,放大1倍。

3 系统测试与分析

3.1 测试工具

测试工具包含GOS-6031 30 MHz双踪示波器,Agilent34401A 6位半数字电压表。

3.2 测试结果

3.2.1 积分波形输出

经测试调整后未发现明显失真。

3.2.2 电压测量

采用6位半电压表进行校准,结果如表1所示。

由以上数据可以看出,设计已完全达到了误差小于等于O.05%±5个字和分辨率为O.1 mV的要求。

4 结语

该设计较好地实现了所要求的功能,从测试结果看,测量误差较小、分辨率较高。由于采用了CPLD在很大程度上减小了环境干扰。当然该设计还有需要改进的地方,如可增加自动校零功能等。

技术专区

- 联发科与中国移动完成NB-IoT R14速率增强测试

- 测试设备结构四种类型 测试测量该考虑的问题

- linux平台下编写虚拟仪器系统设计

- 电能质量监测装置在电网中的应用

- 聊聊电气安全 无线热成像万用表的重要性