作为赛灵思的现场工程师,我常常问这样的问题:我们是否能够提供一款其功能可满足客户所有独特设计要求的DSP内核。有时候内核会太大,太小或者不够快。有时,我们会开发一款能确切满足客户需求的内核,并迅速以COREGeneratorTM商标推出。不过即便在这种情况下,客户仍然想要一套特定的DSP功能,而且刻不容缓。在这些情况下,我常常建议他们使用我们器件中的插值查找表来定制他们的DSP功能。

查找表 (LUT) 实质上是一个存储元件,能够根据任何给定的输入状态组合,“查找”输出,以确保每个输入都有确切的输出。采用LUT来实现 DSP功能具有一些重大优势:

您可用诸如MATLAB®或Simulink®等高抽象层编程语言改变LUT内容。

您可以设计一项DSP功能来运行那些采用离散逻辑运算将极度困难的数学函数,比如 y=log(x)、y=exp(x)、y=1/x、y=sin(x) 等。

LUT还可轻松执行在可配置逻辑块 (CLB) 芯片,以及嵌入式乘法单元或DSP48可编程乘法累加 (MAC) 单元方面可能要求过多FPGA资源的复杂数学函数。

不过,以这种方式使用LUT当然也会存在一些弊端。当您使用LUT来实现DSP功能时,您必须使用块RAM (BRAM) 元件。若执行函数y=sqrt(x)(其中x 表示16位输入,y 表示18位输出),每个变量则需要约64个18KBBRAM单元。如果,比如说,您的目标是实现小型化Spartan®器件,或者您有太多的运算需要执行,无法为每个变量省出64个BRAM单元,建议您放弃这种需要如此大量BRAM单元的方法,从系统架构的角度来看,这种方法代价太大。

插值LUT方法不仅具有LUT方法在实现DSP功能时所带来的各种优势,而且无需使用太多BRAM单元。采用这种方法,您可以使用来自容量较小的LUT (比如,1000字 LUT)的连续输出,线性地对其内插,以模拟更大容量的LUT。这样,您就可以实现比1000 字 LUT更高的数值分辨率。此外,通过这种方法,仅需 1 个 BRAM、1个嵌入式乘法器(或DSP48),以及少数几个CLB芯片便可实施控制逻辑,因此LUT的使用成本变得更加合理化。而且,从信噪比的角度来看,其数值精度也是非常让人满意。

当然,应用插值LUT (ILUT) 方法需要一定的技巧。举例来说,采用该方法执行y=sqrt(x)函数时,可以清楚地显示ILUT在面积占用、时序和数值精度方面的性能。我们先大致看一下这个示例,然后我再讲解部分实例,说明如何使用这种方法来满足客户截然不同的需求,比如让传递函数呈非线性的传感器实现线性化,以及实施自适应有限脉冲响应(FIR) 滤波器以消除合成孔径雷达 (SAR)图像上的斑点噪声。

使用System Generator for DSP进行设计

为在赛灵思FPGA上实施DPS算法,我借助了采用MathWorks Simulink基于模型设计方法的System Generatorfor DSP设计与综合工具。System Generator得益于赛灵思在Simulink 环境中的DSP模块组,可自动调用COREGenerator为DSP构建块生成高度优化的网表。Simulink是一种双精度浮点设计工具,而SystemGenerator则是一款定点运算工具。不管怎样,您只要将这两种工具协同使用,就可以定义每个信号的总位数以及每个信号的二进制位置,从而在定点运算中巧妙处理分数。仿真结果周期精确、位真,因此您可以方便地将它们与MATLAB脚本或Simulink模块生成的浮点参考值相比较,以检查量化误差。

图1显示了System Generator中ILUT方案的顶层结构图。为让这个方法尽可能一般化,假设nx=16位中的输入变量 x的取值范围为0≤x<1,因此其格式为“无符号16位加上二进制点右边的16 位”,也称为Ufix_16_16格式。最高有效位 (MSB)和最低有效位 (LSB) 模块分别对应输入数据nb=10的最高位和nx-nb=6的最低位。这些信号被命名为x0和dx。y=sqrt(x)输出则以ny=17位二进制数表示,格式为:Ufix_17_17。

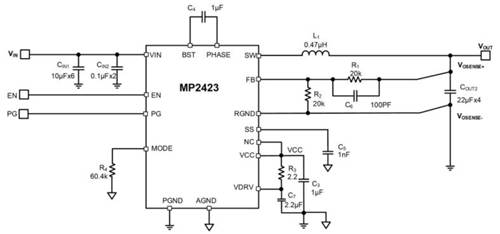

图2显示了1000字小容量LUT通过双端口RAM模块的部署步骤。由于该模块系只读存储器,布尔常数模块We_const强制将写入归零。信号X0和X0+1则用作ROM表上后续的两个地址。Data_const模块的零常数定义了任何ROM字的大小(即本例中的ny)。

下面的公式显示了以x0为x的最高有效位的情况下,如何在两个已知点(x0,y0)和(x1,y1)之间插入坐标为(x,y)的点:

注意X1和X0是这个小容量LUT的相邻地址,它们之间只隔了一个最低有效位。由于这个小容量LUT的地址空间为nb 位,那么该LSB的值为2-nb。

内插步骤见图3。“Reinterpret”模块在不改变二进制表示法的情况下,可改变dx=x-x0信号。其重置了二进制小数点(从UFix_6_0到UFix_6_6格式),并输出nx-nb位二进制数的一个分数,从而计算出 (x-x0)/2-nb 的值。

从硬件角度来看,这些模块什么都不占用。总的来说(且根据我们通过ILUT方法应用的函数类型),如果y1=0且y0=0,我们可以强制y1-y0=1,这样我们就可以得到1/2-nb而不是0。我们采用Mux、RaTIonal、Constant和Constant1模块来执行这项工作。剩下的Mult、Add和Sub模块则执行线性内插公式。在本例中,我强制Mult模块的输出信号为17位分辨率,而非理论上要求的23位,因为总体数值精度对本试验来说已经足够。此外,由于y-sqrt(x)函数呈单调递增,因此所有结果都无符号。换句话说,不同的函数需要对数据类型进行不同的精心调整,但不会与图3所示的原理相去甚远。

假定我们以Spartan-3E 1200(fg320-4)为目标器件,现使用ISE设计套件和System Generator for DSP 10.1 SP3版工具对其进行布局和布线,结果其所占用的FPGA资源的总体情况如下:

该设计完全流水线作业,可以在任何一个时钟周期提供新的输出。时延为10个时钟周期,最大数据速率达194.70MSPS(每秒百万采样数)。从数值精度来说,对1000或2000字ILUT而言,参考浮点结果与System Generator forDSP定点输出的量化误差之间的比值,即信噪比分别为 71.94dB或77.95dB。

除ILUT外,我们还可应用赛灵思System Generator for DSP提供的Reference MathBlockset(参考数学模块组)中的CORDIC SQRT模块。在本例中,总时延为37个时钟周期,最大数据速率达115.18MSPS,区域资源占用为940片触发器,总共有885个四输入LUT,560个占用的芯片以及两个MULT18x18嵌入式乘法器。信噪比为40.64dB。这些结果显示CORDIC是实施定点数学运算的理想方法,但ILUT在许多方面更加出色。

技术专区

- mybatis动态sql详解

- 用VHDL语言设计数据传输系统中的HDB3编码器

- 裸机程序如何驱动硬件?看前辈是怎么说的

- 应用面向对象编程SoC原则的典型示例

- 嵌入式开发之java常用开发工具介绍