目前,图像监控系统大多采用PC和视频采集卡作为系统主要部分,基于嵌入式技术的图像监控系统设备在我国还只是起步阶 段,没有成熟的产品应用。这一现状的根本原因就是我国在开发这类产品时,没有统一的开发标准和共用的开发平台,而且没有可靠的功能和性能测试标准,各个企 业的开发技术力量分散,极大的影响了该类产品开发的效率和可靠性。而制造出来的产品同国外同类产品相比,功能相差太大,没有竞争力,市场基本上被国外公司 所占领。因此,开发一个该类嵌入式系统势在必行。

系统总体方案

为了实现自动图像报警和图像采集,本文设计了动体检测算法,这是因为绝大多数情况下我们只对监控区域中运动的物体感兴 趣,这样可以过滤掉只包含静态背景的图像,从而降低了对有限的嵌入式硬件资源的消耗。由于活动物体大多是人,而且这也是图像监控的目标,为此加入了人体信 号探测器,用以辅助动体检测,以达到降低图像报警误报率的目的。本系统主要集成了图像采集、控制和存储等器件或芯片,组成了以FPGA为控制核心的实时图 像监控系统。系统的总体方案如图1所示。

系统工作流程为:系统上电后,FPGA从外部EEPROM自动加载程序,I2C模块对CIS进行初始化工作参数配置。 CIS向FPGA输入图像数据信号,FPGA将采集的原始数据(RAW)转换成RGB格式,帧缓冲模块(Frame Buffer)每次将相邻两帧图像数据写入SDRAM,然后比较这两帧图像的差值,如果差值大于设定的阈值,并且人体探测器输出高电平,就认为检测到了外 界场景的运动,系统会自动将捕获的图像输出到SD卡进行存储。图2给出了系统的工作流程。

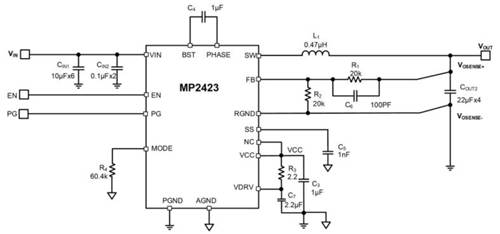

图3 电源电路原理图

系统硬件设计与实现

图像监控系统处理的数据量较大,同时还要满足实时性要求,因此板载电路需要选用容量较大,速度较快的器件。本系统采集的 一帧图像分辨率大小为640&TImes;480,色深是24位,检测时需要在SDRAM缓存两帧,因此SDRAM的容量必须大于1.8M字节 (640&TImes;480&TImes;3&TImes;2=1843200字节),由于每个像素位宽为24位,同时NIOS是32位的处理器,所以SDRAM的位宽最好是32位。外部提 供给FPGA的晶振频率必须大于CIS的像素时钟25MHz。考虑到检测算法需要较多的逻辑资源,因此FPGA的片内LE要很丰富,另外FPGA的管脚必 须要满足外部器件连接的要求,在本系统中要实现所有器件的I/O口相连,FPGA的I/O管脚必须大于150个。由于电路原理图较多,这里只给出其中的一 部分。

主控制芯片电路

本系统选用的Cyclone系列FPGA器件的具体型号是EPlCl2Q240C8。逻辑资源达12060个逻辑单元 (LE,Logic Elements),片内RAM的容量为239616bits。完全可以满足图像采集的设计要求。其内核供电采用1.5V、0.13um工艺,功耗较低。 Cyclone器件支持各种单端I/O接口标准,如3.3V、2.5V、1.8V、LVTTL、LVCMOS、SSTL。Cyclone器件具有两个可编 程锁相环(PLL)和八个全局时钟线,提供健全的时钟管理和频率合成功能,实现最大的系统性能。Cyclone器件具有高级外部存储器接口,允许设计者将 外部单数据率(SDR)SDRAM,双数据率(DDR)、SDRAM和DDR FCRAM器件集成到复杂系统设计中,而不会降低数据访问的性能。Cyclone系列FPGA器件基于一种全新的低成本架构,从设计之初就充分考虑了成本 的节省,因此可以为价格敏感的应用提供全新的可编程的解决方案。

电源电路

一般而言,FPGA器件出于芯片设计、多电平接口的需要,电源都分为两组:VCCINT和VCCIO,即内核电源和 I/O电源,随着芯片内部连线尺度的逐渐减小,核心电源电压和接口电压也越来越低。本设计中EPlCl2器件的VCCINT为1.5V,VCCIO为 3.3V。目前总的来说有三种电源解决方案,分别是线性稳压器电源(LDO)、开关稳压器电源和电源模块。

LDO线性稳压器适用于降压变换,具体效果与输入/输出电压比有关。从基本原理来说,LDO根据负载电阻的变化情况来调节自身的内电阻,从而保证稳压输出端的电压不变。其变换效率可以简单地看作输出与输入电压之比。

由于采用线性调节原理,LDO本质上没有输出纹波。与LDO相比,DC/DC调整器输出纹波电压较大、瞬时恢复时间较 慢、容易产生电磁干扰(EMI)。系统电源输入电压为5V,3.3V电压供电部分采用了ASl084;此外,对于FPGA的PLL工作需要的1.5V电源 部分,采用AMS1117-1.5 LDO来实现。

由于Altera的PLL是模拟电路实现的,其对电源噪声比较敏感,所以在设计PCB的时候,对给PU的供电部分要做一些特殊的处理。即使在设计中没有用到PLL也必须给其供电。

本系统中选用的EPlCl2F400C8芯片的输入输出接口电压为3.3V,内核电压降低到1.5V,这样可以降低功 耗,有利于系统的稳定,但也给电源供电和其它芯片的选择带来了麻烦,系统中其它芯片的接口电压必须为3.3V,至少也要兼容3.3V,电源设计中需要考虑 的主要问题是功率是否满足的问题。

技术专区

- 基于FPGA的嵌入式实时图像监控系统浅析

- 随着RRAM成为主流,大容量嵌入式内存支持的高智能化系统解决方

- 英飞凌推出第二代适用于各式LIN伺服电机控制应用的嵌入式功率

- 你想知道的Ocaml语言

- 来了解一下Groovy语言