上一章介绍了时钟产生的几种方式以及每种方式对应的应用场景。今天讲一下产生的时钟是怎样传递出去到每个应用这些时钟信号的器件,你可以把这个过程看作是人体的脉搏。我们分几种场景来看:

多数的逻辑功能都依赖时钟的边沿对数据进行判决

我们先说一下器件内部时钟的使用:

比如MCU - 在器件内部直接产生或者配合外接的振荡电路产生,就地使用,你不需要关心这些时钟信号在内部是如何使用的,那是IC设计工程师的事情,他们做的事情就类似FPGA逻辑编程一样,不过对于使用这些器件的工程师 - 软件工程师、系统工程师,不需要关心这些细节。你只需要编写程序,让自己要实现的功能通过一条条的指令去执行就可以了。

MCU接上振荡电路动起来,你只需要专注于编程就可以了

比如FPGA - 几乎内部所有的功能都需要不同频率、不同相位时钟的参与,而这些时钟可能都来自于同一个时钟源,因此时序(Timing)可以说是FPGA工程师最头疼的问题 - 无论是最基本的时序逻辑还是状态机,Debug的工作重心其实就是查找时序上出现的问题。在FPGA使用时钟过程中你可能需要应对以下的几个问题:

通过内部的逻辑产生你所需要的不同频率、不同相位的时钟信号

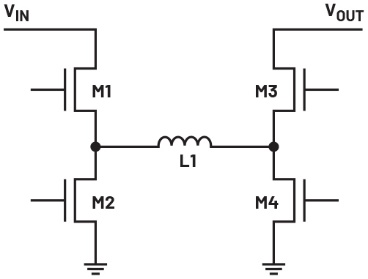

通过PLL生成高速的时钟,毕竟外接或者自身振荡产生的时钟信号频率不会太高,而FPGA内部的逻辑需要更高速地运行,因此目前主流的FPGA都会自带几个PLL甚至DLL

通过PLL进行相位的调整。内部的逻辑门一定会有传输延迟,在你需要相位精确要求的逻辑电路可以使用PLL来获取你所需要的相位时钟

通过PLL做精确的相位调整

通过PLL也可以进行时钟占空比的调整

通过PLL也可以消除参考时钟上的噪声和抖动(jitter)

时钟信号的相位和周期抖动示意