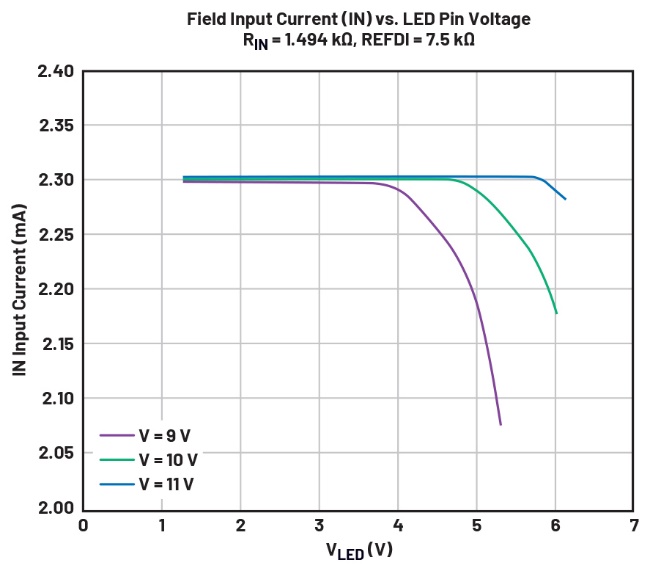

交流信号可由多种信号源产生,其中不少信号源与诸如ttl等最常用的接口电压不兼容。人们通常使用电容来耦合ac信号,因为电容耦合能滤除直流分置电平。但是电容耦合有时不适用,这是因为被耦合的信号电压在地电平上下摆动,所以必须增加直流偏置,以使被耦合的信号与接口电压兼容。此外,被耦合的信号所含的直流电压分量vdc随脉冲宽度变化而变化。当被耦合的信号振幅较大时,这种直流变化会对接口电压产生干扰。本电路能测量直流偏置,对电容耦合的信号进行相应补偿,并增加直流电平调节功能,从而能实现信号接口(图1)。r1和c2构成低通滤波器(f3db=0.312hz),用以测量输入信号的直流分量。其转移方程如下:

当r1+r2=r3和rf=rg时,vdc就转移至输出信号va,这是由于vdc被乘以1/2(2)=1,即增益为1。相同电阻值的输出电压包含了vref;这样,输出信号的电平就被移位了vref,而不是vref加上vdc。当输入信号的占空比变化,而不是输出电压随占空比变化时,运算放大器使输出电压电平保持恒定不变。vdc的增益必定为1,以便抵消交流耦合后的电压漂移。参考电压的增益可能大于1。例如,若r1+r2=3r3和rf=3rg,则直流分量为1/4(4)=1,而参考电压增益为3/4(4)=3。vref可能为正电压也可能为负电压,因此可以用本电路来获得ttl、cmos或ecl逻辑电平。c1和r4构成的时间常数必须足够大,以便使最低频率信号能够无失真地通过。只要运算放大器能驱动r4而不损失过多信号振幅,对r4的阻值没有严格要求。在有些情况下,可以将r4的阻值设为消除近端反射所需的驱动点阻抗。本电路可以按照配置情况方便地耦合400mhz数据,但是数据率取决于由r4和被驱动电路输入阻抗所构成的时间常数。

图1本电路是一种通用的交流信号电平移位器;它符合任何一种接口标准。