在 9 月 19 日于北京举行的英特尔精尖制造日上,英特尔在其展示区域和主题演讲上展示了五款晶圆。

这是英特尔首次公开展示这五款晶圆,彰显了我们在制造领域取得的巨大进步。

五款全球首次展出晶圆

英特尔 10 纳米cannonlake

英特尔 10 纳米 arm 测试芯片

英特尔 22ffl

14 纳米展讯 sc9861g-ia

14 纳米展讯 sc9853

英特尔 cannonlake 10 纳米

英特尔 10 纳米制程工艺:

• 不仅拥有全球最密集的晶体管和金属间距,还采用了超微缩特性,这两大优势保证了密度的领先性

• 比竞争友商的“10 纳米”技术领先了整整一代

• 计划于 2017 年下半年开始生产

• 超微缩可释放出多模式方案的全部价值,使得英特尔得以继续摩尔定律的经济效益

英特尔 10 纳米cannonlake

英特尔与arm在10nm的合作

取得了长足的进步:

1. 英特尔 10nm cpu测试芯片流片具有先进的arm cpu核, 使用行业标准的设计实现, 电子设计自动化 (eda) place and route工具和流程 ,性能高达3ghz以上

2. arm同时正在开发高性能存储器、逻辑单元和cpu pop套件,以进一步扩展下一代arm cpu在英特尔10nm技术上的性能水平

arm cortex a75: intel 10nm 测试芯片

• 在12周内从rtl 至首次 tape out

• 标准英特尔10nm工艺

• 最新的软件测试结果 > 3.3ghz

• 250uw/mhz

英特尔 10 纳米 arm 测试芯片

英特尔10纳米制程:

通过超微缩技术实现业界最高的逻辑晶体管密度

英特尔10纳米工艺采用第三代 finfet(鳍式场效应晶体管)技术,相比其他所谓的“10纳米”,英特尔10纳米预计将会领先整整一代。英特尔10 纳米工艺使用的超微缩技术 (hyper scaling),充分运用了多图案成形设计 (multi-patterning schemes),并助力英特尔延续摩尔定律的经济效益,从而推出体积更小、成本更低的晶体管。英特尔10纳米制程将用于制造英特尔全系列产品,以满足客户端、服务器以及其它各类市场的需求。

英特尔10纳米制程的最小栅极间距从70纳米缩小至54纳米,且最小金属间距从52纳米缩小至36纳米。尺寸的缩小使得逻辑晶体管密度可达到每平方毫米1.008亿个晶体管,是之前英特尔14纳米制程的2.7倍,大约是业界其他“10纳米”制程的2倍。

相比之前的14纳米制程,英特尔10纳米制程提升高达25%的性能和降低45%的功耗。相比业界其他所谓的“10 纳米”,英特尔10纳米制程也有显着的领先性能。全新增强版的10 纳米制程——10++,则可将性能再提升15%或将功耗再降低30%。

英特尔晶圆代工业务通过两个设计平台——10gp(通用平台)和 10hpm(高性能移动平台),向客户提供英特尔10纳米制程。这两个平台包括已验证的广泛硅ip组合、arm 库和 pop 套件,以及全面整合的一站式晶圆代工服务和支持。

英特尔22ffl(finfet 低功耗)平台

卓越集成能力

一流的 cpu 性能,主频超过 2 ghz

超低功耗,漏电率降低 100 倍

22 纳米+ 制程,每平方毫米 1,780 万个晶体管

全面的 rf 设计支持

快速上市速度

行业最易使用的 finfet 制程

成熟生产平台,具备业经验证的 22/14 纳米特性

经过芯片验证的移动/物联网 ip 组合

arm 库和 pop 套件

英特尔架构处理器 ip 套件

交钥匙代工服务与支持

cost-effective的设计

与业界28纳米的平面(planar)工艺相比在成本上极具竞争力

单模式互联和宽泛的 dfm 规则

无复杂的衬底偏压要求

理想应用

入门级/经济型智能手机

车载

可穿戴设备

英特尔22ffl(finfet 低功耗)平台

英特尔22纳米finfet低功耗(22ffl)技术:

面向主流市场的finfet技术

英特尔自2011年发布代号为ivy bridge的处理器以来,一直在量产22纳米finfet(鳍式场效应晶体管),而随着2014年代号为broadwell的处理器发布,第二代14纳米finfet也开始量产。基于多年22纳米/14纳米的制造经验,英特尔推出了称为22ffl(finfet低功耗)的全新工艺。该工艺提供结合高性能和超低功耗的晶体管,及简化的互连与设计规则,能够为低功耗及移动产品提供通用的finfet设计平台。

与先前的22gp(通用)技术相比,全新22ffl技术的漏电量最多可减少100倍。22ffl工艺还可达到与英特尔14纳米晶体管相同的驱动电流,同时实现比业界28纳米/22纳米平面技术更高的面积微缩。

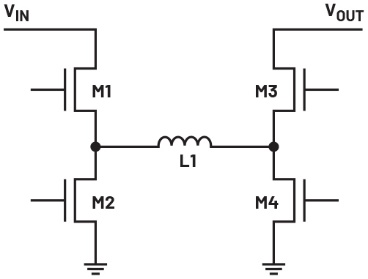

22ffl工艺包含一个完整的射频(rf)套件,并结合多种先进的模拟和射频器件来支持高度集成的产品。借由广泛采用单一图案成形及简化的设计法则,使22ffl成为价格合理、易于使用可面向多种产品的设计平台,与业界的28纳米的平面工艺(planar)相比在成本上极具竞争力。

22ffl器件:

• 高性能晶体管

• 低1/f噪声

• 超低漏电晶体管

• 深n阱隔离

• 模拟晶体管

• 精密电阻

• 高压i/o晶体管

• mim(金属-绝缘体-金属)电容

• 高压功率晶体管

• 高阻抗衬底

迄今为止,英特尔已交付超过700万片finfet晶圆,22ffl工艺充分利用这些生产经验,达到了极高的良品率。

英特尔晶圆代工业务(intel custom foundry)通过平台向客户提供22ffl工艺,该平台包含多种已验证的硅ip组合以及全面集成的一站式晶圆代工服务和支持。

激动人心的22ffl新技术适用于低功耗的物联网和移动产品,它将性能、功耗、密度和易于设计的特性完美结合。

经过展讯验证的

英特尔晶圆代工业务 14 纳米平台

展讯的 sc9861g-ia 和 sc9853i 移动 ap 均使用英特尔的 14 纳米低功耗平台制造而成。

这两款移动 ap 分别于 2017 年 3 月和 8 月推出,同时还使用了英特尔 airmont cpu 架构

英特尔的 14 纳米平台适用于制造需要高性能和低漏电功耗的产品

第二代 finfet 技术

行业领先的 ppa,每平方毫米 3,750 万个晶体管

一流的 cpu 性能,主频超过 2.5 ghz

快速上市速度

业经验证的 14 纳米 hvm(大规模量产)技术

经过芯片验证的移动/网络 ip 组合

交钥匙代工服务与支持

两个平台满足您的全部产品需求

通用 (gp)

低功耗 (lp)

理想应用

主流移动

数据中心

经过展讯验证的

英特尔晶圆代工业务 14 纳米平台

英特尔 14 纳米制程:

打造极速、节能产品

英特尔14纳米制程采用第二代 finfet 技术,提升性能并降低漏电功耗,从而支持一系列广泛的产品。英特尔14纳米制程正处于量产阶段,用于制造包括高性能服务器、fpga以及低功耗个人计算设备、移动设备、调制解调器和物联网设备在内的各类产品。

14 纳米制程的晶体管鳍片更高、更薄且更加密集,从而提升了密度和性能。这些改进的晶体管需要的鳍片数量更少,进一步提升了制程的总体密度。晶体管栅极间距从90纳米缩小至70纳米,最小互连间距从80纳米缩小至 52 纳米,从而让晶体管密度到达每平方毫米 3,750 万个晶体管的标准。通过采用超微缩技术,英特尔14纳米制程相比之前的 22 纳米制程实现了非常显著的微缩,其中逻辑单元面积微缩为此前的37%,晶片尺寸微缩超过此前的一半。

相比于业界其他的14/16/20纳米制程,英特尔14纳米制程的密度是它们的约1.3倍,这极大降低了单个晶体管成本(cpt)。业界的“10 纳米”制程预计于2017年的某个时段出货,而其晶体管密度仅与2014年便已开始出货的英特尔14纳米制程相当。

14 纳米制程超微缩的一个关键因素是引入自校准双图案成形 (sadp),相比业界的曝光-蚀刻-曝光-蚀刻 (lele) 方法,它在晶体管密度和良品率上更有优势。

英特尔不断改进14纳米制程的性能和功效。14 纳米制程的持续优化使其性能比最初的14 纳米制程可以提升多达 26%,也可以在相同性能下降低50%以上的有效功耗。英特尔14+制程的性能比最初的14纳米制程提升了12%,而英特尔14++制程在此基础上又将性能提升了24%,超过业界最佳的其他14/16纳米制程20%。

英特尔14纳米制程还包含一整套可支持并增强各种产品设计的器件。这些器件包括高阻衬底、高 q 电感器、高密度 decaps、深n阱(deep nwell)、精密电阻器、低漏电功耗及长 l 晶体管,以及射频晶体管模板和建模。

英特尔14纳米制程正在美国俄勒冈州、亚利桑那州和爱尔兰的工厂进行量产,迄今已出货 4.734 亿件。英特尔代工业务通过两个设计平台——14gp(通用)和 14lp(低功耗),向客户提供英特尔14纳米制程。这两个平台包括广泛的硅验证ip组合以及全面集成的交钥匙代工服务和支持。

来源:电子产品世界