随着科学技术的发展,IC产业得到了快速的提升,IC的制造复杂度也变得更加严格。IC测试也面临了很多的挑战,最为典型的就是测试的精确度及稳定性。尤其在量产ATE测试时表现更为严重,那我们如何去避免由于测试不稳定而导致反复重测而浪费大量测试时间呢?

本文就IC测试的基本参数:电压、电流、时间、THD等的测试进行深入分析,并举以实例来说明如何解决此类问题,以供广大测试工程师参考。

电压测试问题

在IC的测试中,电压的测试是所有测试参数中最为常见的一种参数,尤其是模拟芯片的测试,电压测试更显常见及重要,如:LDO、LED驱动、音频功放、运放、马达驱动等很多类型的模拟芯片都含有电压参数的测试,而且都是其主要性能参数。另外,也有很多其他的参数都是通过电压的测量来间接得到的,如增益(Gain)、电源电压抑制比(PSRR)、共模抑制比(CMRR)等。工程师们在调试中也经常会遇到电压测的不精确或者不稳定的现象,对于测试不精确的问题,目前主要采用correlaTIon的办法,来调整测试的误差,但这种方法对于线性的芯片尚可使用,但对于非线性的芯片却无用武之地。针对测试不稳定的问题,大多采用多次测量取平均值的办法来解决,但这种办法也是治标不治本,同样会给产品的质量带来隐患。那么如何解决电压测试的这些问题呢?以下将具体分析产生这些现象的具体原因,并针对这些原因阐述一些解决办法。

芯片工作状态未完全建立或有震荡

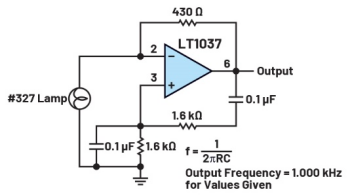

一般在开发测试程序之前必须了解所测试的芯片的功能及性能参数,这样在开发及调试程序时才能心中有数,比如测试LDO的输出电压参数,你必须清楚:在当前的输入及输出滤波电容之下,它的输入电压加上之后,输出电压需要多长时间才能达到稳定,而你在程序中设定的等待时间必须大于这个稳定时间,这样才能做到测试的准确且稳定。当然LDO的输出稳定时间一般都在微秒级(几十到上百微秒),所以调试时不太会遇到此类问题,但有的时候我们需要测试芯片内部的基准电压,但又没有办法直接进行测试,只能通过其他的引脚间接测试,如图1为LED驱动芯片的部分线路图,

图1

我们要测试芯片内部Vref的电压,但又没有直接的引脚出来,所以只能通过测试VO端的电压进行间接测试,但是需要注意的是:如果VO端悬空,没有任何电流流出,那么它上面的MOS管则不能正常导通工作,EA1的反馈回路也不能正常建立,而导致VO端的电压也不确定,此时测试的VO电压将不能代表Vref的电压。所以在测试时,我们必须给VO一定的负载让MOS管及EA1能够正常工作,这样才能正确测试Vref的电压。

芯片工作状态的建立,有时需要比较长的时间,如图2为一音频功放(LM4990)的功能框图及典型应用线路图,

图2

我们在ATE测试时会测试一些静态直流参数,如bypass、Vo1、Vo2端电压值,当你仔细研读此芯片的手册,你会发现在电源电压为5V、Cbypass为1Uf时(注意不同的电源电压及Cbypass电容,其稳定时间也是不同的),bypass端的电压需要至少100ms才能达到稳定,而Vo1、Vo2端的电压又受bypass端电压的影响,所以要想稳定且准确的测试这些直流参数,必须要在芯片上电之后等待100ms以上再进行测试(必须考虑不同批次芯片间的差异,所以在实际测试中的等待时间可在120ms左右),但对于量产测试,测试时间的长短将直接影响到测试效率及测试费用,我们必须缩短测试时间!那么如何来解决这个问题呢,一般我们可以采用如下两种办法:

第一,可以减小Cbypass的电容,这样同样的充电电流及电压,充电时间会随着电容的减小而减少,可以使用0.1uF或者更小的电容来替代,此时有些读者可能会说:这样做肯定会影响到后面的交流参数(如THD)的测试,没错!肯定会有影响!那么又如何来解决呢?其实很简单,也可以有两种解决方案:

1、通过测试评估,适当调整在0.1uF时的交流参数的测试规范,当测试要求不高时可采用此方案;

2、通过外加继电器来选择测试直流及交流参数时的电容值,但是继电器的连接方式也是很有讲究的,不然也会对交流参数有影响,这在后面的段落中再详细阐述。

第二,可以采用预充电的方式对Cbypass进行提前大电流充电,如果bypass端在电源电压为5V时正常情况下是2.5V左右,我们可以预充电到2.3V,这样同样可以节省很多时间,但这种解决办法必须注意一个问题就是:不要在充电的同时给bypass端带来额外的干扰,而导致芯片不能正常工作。

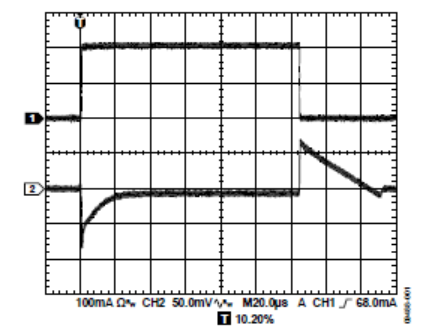

图3

震荡在芯片调试时也是比较常见的现象,由此给芯片测试也带来诸多问题,引起震荡的原因有很多:输出容性负载的大小、阻抗不匹配、不当的反馈回路等,如图3为一款LDO(TL431)芯片手册中的一幅电性能特性曲线及测试图,图中明显规定了输出容性负载CL的大小范围,但是我们在实际调试中可能没有注意到这一点,如果选用的输出电容不是在芯片稳定所需要的容值范围之内,那么输出就会产生震荡,导致输出测试不准且不稳定。所以在此再次提醒大家:在调试之前务必将芯片性能做到比较详细的了解,以免在后期的调试中浪费大量的时间。

另外震荡不光是在芯片正常工作时发生,在静态时也有可能发生。尤其当你测试放大倍数比较高的运放时,此时的输入引脚要特别注意,必要时要进行隔离,以免引入不必要的噪声而导致输出产生震荡。

技术专区

- smd封装是什么意思_smd封装有哪几种类型

- cob封装为何迟迟不能普及

- 一文看懂cob封装和smd封装区别

- Wavecrest双引擎技术实现信号完整性测试

- 利用逻辑分析仪和DSO解决信号完整性问题