高帧频的视频信号不同于普通视频信号,如果采用模拟信号方式传输,它的模拟带宽达到了几十兆甚至一两百兆,这样很难实现远距离传输。而光纤传输容量大、质量高和不易受干扰等特点,在高速数字传输系统中得到了广泛应用。目前国内外针对普通视频信号的光纤传输系统已相当多,而对非标准的高帧频视频信号光纤传输系统少有报道,特别是两路或多路高帧频视频的单根光纤传输实现则未见报道。

在本文中需要实现两路256&TImes;256像素每秒1000帧高速视频信号远距离传输。对于高帧频摄像机,由于它帧频很高,通常采用多路并行的信号输出方式降低数据率,最后通过复用合成为视频信号。为实现远距离传输,文中提出采用数字光纤的复用、解复用和计算机PCI技术实现两路高帧频视频设备产生的15MBps&TImes;40路数字信号的传输与视频信号的合成及计算机实时显示。

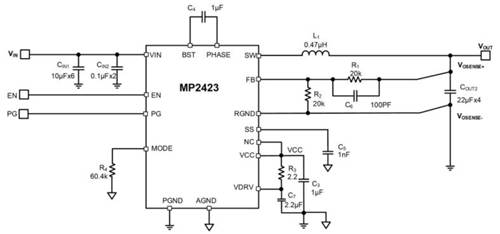

1 系统原理和结构

高速视频信号的光纤传输系统主要包括复用、光发射、光接收、解复用、控制电路和PCI传输接口等部分。图1为系统光发射部分工作原理图。

从高速视频采集获得的40路15MBps的数据首先经过XC9572内的2:1复用,形成20路30MBps的二级复用数据提供给HDMP-1022,由其完成信道编码、转换成600MBps的PECL串行数据,驱动光发射模块,完成数据的光纤发射。图2为光接收部分原理图。

解复用芯片HDMP-1024从光纤接收模块接收到的600MBpsPECL数据中提取出20路的并行数据和30MHz的时钟信号,再由XC9572完成二级解复用,同时也为FIFO及PLX9052组成的PCI传输卡提供时序信号,计算机通过PCI总线获得实时高速视频采集数据,并予以显示和处理。

2 硬件设计

系统的硬件设计主要包括光纤传输单元、PCI传输单元和控制单元三部分。

2.1 数字光纤传输单元设计

数字光纤传输单元主要完成串并行数据的复用与解复用功能。设计中采取数据通信中的CIMT(CondiTIonal-Invert Master TransiTIon)信道编码方式对数据进行编码。图3显示CIMT码的格式。

CIMT码有三种帧形式:数据帧、控制帧和填充帧。数据帧和控制帧的格式如图3(a)所示,可以发送任意需要传送的数据和控制信息,每一帧都以C-Field(Coding Field)开始,其后接着D-Field(Data Field)。其中D-Field组成的数据位可以是十六位或二十位,本系统采用二十位数据;控制位(C-Field)由四位数据码组成,接收端可以此提取并锁定数据的类型与状态。填充帧是在发射端没有数据信号时以及发射端和接收端建立连接时产生。在三种帧的主瞬变点处是接收端恢复时钟信号的参考点。本系统中选用Aglient公司的HDMP-1022和HDMP-1024作为CIMT码的复用与解复用主要芯片,HFCT-5208作为光发射和光接收器来实现点对点的光纤传输设计。

在光发射端设计中采用HDMP-1022的Double-Frame模式实现40路数据的传输,通过二级复用扩展其并行数据的容量为40路。数据在同一时钟控制下同时被复用成一路的高速信号,同时生成另一路按位取反的信号,最后通过其CIMT编码器输出推动光发射器。图4为以Double-Frame方式复用发射的时序图。其中CLOCK(15MHz)是单路数据采集时钟,FLAG表示奇偶场,CAV和DAV表示数据帧和控制帧的控制位,C0~C39表示输入的40路信号,D0~D19是CIMT码的D-Field数据,STR-BOUT(30MHz)为芯片锁相后的倍频时钟。

在光接收端部分光接收器将获得的光信号转变为高速电信号并发送给HDMP-1024,由它解复用后提取参考时钟信号STRBOUT(30MHz)、数据信号C0~C39,以及其他的状态控制信号和数据时钟RCLK(15MHz)。图5为Double-Frame光接收端时序图。

图3

2.2 PCI传输单元设计

为实现高速视频信号的实时记录,设计中利用了PCI总线技术,PCI控制芯片采用PLX9052,它与FIFO相结合可以实现最高数据传输速率120MBps数字量输入。

PLX9052符合PCI2.1规范,支持低成本从属适配器。内部包括一个64字节的写FIFO和一个32字节的读FIFO,通过读写FIFOs,可实现高性能的突发式数据传输;其局部总线与PCI总线的时钟相互独立,局部总线的时钟频率范围为0~40MHz,PCI的时钟频率范围为0~33MHz;可以通过串行EEPROM提供PCI总线和局部总线的部分重要配置信息。PLX9052支持突发式内存映射传输和单周期的内存或I/O映射传输,利用32字节的直接从设备读FIFO和64字节的直接从设备写FIFO,映射在PCI内存和I/O空间中的地址由PCI基址寄存器设置。而且,局部映射寄存器允许将PCI地址空间转换为局部地址空间。图6是PLX9052与FIFO相互连接的电路图,FIFO采用IDT公司的IDT72205。

2.3 控制单元设计

整个设计的时序控制单元均由CPLD完成,在光发射端主要提供40路信号的2:1复用、数据的锁存及系统工作的时序信号;在光接收端主要为解复用、FWO和PLX9052提供相应的时序逻辑。本设计选用Xilinx公司的XC9572作为控制单元的核心芯片,结合它的在线编程功能,完成整个系统的时序调试与设计。

结合Verilog语言与原理图(sch)方法,较好地实现了整个系统时序的设计。以下是40路数字信号8:1复用Verilog语言设计代码。

3 软件设计

整个系统软件主要包括PCI传输单元的驱动程序和系统应用程序设计。 Windows下的PCI驱动程序不仅仅包括物理设备的驱动程序,也包括为文件系统等非物理设备编写的虚拟设备驱动程序。在设计中主要针对Windows2000下PCI驱动程序设计。由于Windows 2000禁止用户模式的程序访问I/O端口(Windows 95/98则允许用户程序直接访问I/O端口),直接控制物理设备的驱动程序均为内核模式。而本设计的PCI驱动程序要求对各种硬件资源访问,所以应该选择工作在零级的驱动程序模式。

开发设备驱动采用的主要开发工具是JUNGO公司提供的软件包Windriver。这个软件包提供开发PLX9052有关设备的文档、编译需要的头文件和库文件、调试工具和程序范例。利用其内部定义的可以调用的系统底层服务,如DMA服务、中断服务、内存管理服务、可安装文件系统服务等,结合VC++完成整个PCI设备驱动程序。本设计包括以下几个方面:

(1)PCI设备初始化

PCI设备驱动程序首先实现识别PLX9052器件、寻址PLX9052器件的资源和对PLX9052器件中断的服务。主要调用Windirver软件包内以下函数:

WD_Open(hWD);

PCI_Get_WD_handle(&hWD);

PLX_LocateAndOpenBoard(0x10b5,0x9052,UseInt);

(2)PCI端口地址操作

PCI总线是32位的总线标准,在进行I/O操作时通常要进行双字(DWORD)操作,而在Windows 2000下,系统不允许处于优先级3的用户程序和用户模式驱动程序直接使用I/O指令。任何对I/O的操作都需要借助内核模式驱动来完成。笔者主要调用Windirver软件包内两个函数来完成。

(3)内存的读写

PLX9052与计算机进行数据通信主要采取DMA方式,在Windriver中提供了相应内存读取两个函数,通过对它的调用可实现PLX9052与计算机内存的数据交换。

整个系统的应用程序研制都基于微软公司的VC++开发设计,可用于Windows 2000操作系统下。

整个光纤传输系统利用复用、解复用,结合PCI技术实现了高速视频数字化信号远距离传输及控制、实时显示等功能,传输距离15km,可记录数据量为128K字节。目前已将设计用到相关的测试项目中,并将进一步改进扩大数据的容量及稳定性。