现场可编程门阵列 (FPGA) 具有诸多特性,无论是单独使用,抑或采用多样化架构,皆可作为宝贵的计算资产;但是许多设计人员并不熟悉 FPGA,亦不清楚如何将这类器件整合到设计中。

解决办法之一是深入研究主要供应商提供的 FPGA 架构及相关工具。本文则从 Lattice Semiconductor 产品系列开始着手。

FPGA 选件高级概述

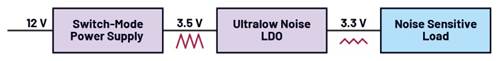

市场上有许多不同类型的 FPGA,每种类型都有不同的功能和特性组合。可编程结构是所有 FPGA 的核心,并以可编程逻辑块阵列的形式呈现(图 1a)。FPGA 结构进一步扩展可包括 SRAM 块(称为块 RAM (BRAM))、锁相环 (PLL) 和时钟管理器等组件(图 1b)。此外,还可以添加数字信号处理 (DSP) 块(DSP 切片)和高速串行器/解串器 (SERDES)(图 1c)。

外设接口功能(如 CAN、I2C、SPI、UART 和 USB)可以实现为可编程结构中的软内核,但许多 FPGA 将其作为硬内核在硅片中实现。同样,微处理器也可以实现为可编程结构中的软内核,或作为硬内核在硅片中实现(图 1d)。不同 FPGA 针对不同的市场和应用提供不同的功能、特性和容量集合。

FPGA 供应商有很多,包括 Altera(被 Intel 收购)、Atmel(被 Microchip Technology 收购)、Lattice Semiconductor、Microsemi(也被 Microchip Technology 收购)和 Xilinx。

所有这些供应商都提供多个 FPGA 系列;有的提供片上系统 (SoC) FPGA(包含硬处理器内核),有的则针对航天等高辐射环境提供耐辐射器件。由于产品系列众多,每个系列提供不同的资源,因此为眼前的任务选择最佳器件可能很棘手。本文着重介绍了 Lattice Semiconductor 推出的器件系列及相关设计工具。

Lattice Semiconductor 的 FPGA 介绍

Lattice Semiconductor 的 FPGA 产品范围覆盖低中端,专注于低功耗器件,应用遍及通信、计算、工业、汽车和消费类等迅速增长的市场,以此帮助客户解决从边缘到云的网络问题。

Lattice 推出了四个主要的 FPGA 系列:

iCE(堪称世界上最小的超低功耗 FPGA)

CrossLink 和 CrossLinkPlus(针对高速视频和传感器应用进行了优化)

MachXO(针对桥接、扩展、平台管理和安全应用进行了优化)

ECP(针对连接和加速应用的通用器件)

此外,Lattice 还推出了诸多设计和验证工具套件,包括 Lattice Diamond 软件(用于 CrossLink/CrossLinkPlus、MachXO 和 ECP 器件)、Lattice Radiant 软件(用于 iCE FPGA 和未来架构)、LatticeMico(用于创建基于软微处理器设计的图形工具),以及 Lattice sensAI 堆栈和神经网络编译器(用于人工智能 (AI) 和机器学习 (ML) 设计)。

传统:ECP FPGA

许多设计人员都认为 Lattice 的 ECP 器件是“传统”FPGA 器件。这类器件采用 10 mm x 10 mm 封装,引脚间距 0.5 mm,最多可包含 85,000 (k) 个四输入查找表 (LUT)。静态和动态功耗较低,协议无关单通道 SERDES 功能器件的功耗低于 0.25 W,四通道 SERDES 功能器件则低于 0.5 W。

除了 SRAM 块、数字信号处理 (DSP) 块、锁相环 (PLL) 和时钟管理器外,ECP FPGA 还具有可编程 I/O,支持 LVCMOS 33/25/18/15/12、XGMII、LVTTL、LVDS、Bus-LVDS、7:1 LVDS、LVPECL 和 MIPI D-PHY 输入/输出接口。

ECP FPGA 的配置单元基于 SRAM,因此与所有其他基于 SRAM 的 FPGA 一样,仅当系统通电时,才能由外部(例如闪存器件、微处理器、微控制器)加载配置。

ECP 器件的一个典型示例是 LFE5UM5G-25F-8BG381C,支持 ECP5 5G SERDES 的 FPGA,采用 10 mm x 10 mm 封装。为了使设计人员能更好地研究和试验 ECP5 FPGA 系列的特性,Lattice 还推出了相应的 ECP5-5G 开发板 LFE5UM5G-45F-VERSA-EVN(图 2)。

体积小巧,但功能强大:Lattice 的 iCE FPGA

iCE 器件是市面上现有体积最小的 FPGA,该系列中最小的器件采用 1.4 mm x 1.4 mm 封装,提供 18 个 I/O。iCE FPGA 采用灵活的逻辑架构,最多可包含 5k 个四输入 LUT,具有高达 128 Kb 的 Lattice 嵌入式 sysMEM BRAM、1 Mb 的单端口 RAM (SPRAM)、高性能 DSP 块,以及可定制 I/O。

iCE FPGA 器件体积小、功耗低(对于多数应用,休眠电流低至 75 µA,有功电流范围从 1 至 10 mA),但功能却很强大。例如,这类器件可实现人工神经网络 (ANN),可用于模式匹配以实现边缘应用中“始终开启”的人工智能。

iCE FPGA 的配置数据存储在非易失性存储器 (NVM) 中,因而属于一次性可编程 (OTP) 器件。尽管如此,器件仍包含基于 SRAM 的配置单元。开发过程中,可将设计直接由外部加载至基于 SRAM 的配置单元来进行测试。设计提交后,即可将其加载至 NVM 中。器件上电后,存储于 NVM 的配置将以并行传输方式自动复制到基于 SRAM 的配置单元中。

iCE 器件的一个示例是 ICE40UL1K-SWG16ITR1K iCE40 UltraLite,它是世界上外形尺寸最小的 FPGA(截至本文发布时),采用 1.4 mm x 1.4 mm 封装,静态功率为 42 µW。代表性开发板包括 HM01B0-UPD-EVN Himax HM01B0 UPduino 扩展板和 sensAI 模块化演示板(图 3)。

该套件基于 UPduino 2.0 开发板,这款 Arduino 外形尺寸的快速原型开发板,具有 iCE40 UltraPlus FPGA 的性能和 I/O 功能。此外,套件还包括 Himax HM01B0 低功耗图像传感器模块和两个 I2S 麦克风。

专用:CrossLink 和 CrossLinkPlus FPGA

CrossLink 和 CrossLinkPlus 系列都是专用 FPGA,除了可编程逻辑和强大的 I/O 功能外,器件规格经过强化,因而可广泛适用于工业和汽车应用。其中包括移动行业处理器接口 (MIPI) D-PHY 高速数据通信物理层标准、相机串行接口 2 (CSI2) 和显示串行接口 2 (DSI2) 内核;封装分别采用 6 mm x 6 mm (CrossLink) 和 3.5 mm x 3.5 mm (CrossLinkPlus)。

与 iCE FPGA 一样,CrossLink 器件的配置数据存储在 OTP NVM 中,也包含基于 SRAM 的配置单元,开发过程中可直接加载进行测试。设计提交后,则将其加载至 NVM 中。器件上电后,数据以并行传输方式自动复制到基于 SRAM 的配置单元中。相比之下,CrossLinkPlus 器件的配置单元基于闪存,因此可根据需要对这些器件进行重新编程;此外,器件还具有不足 10 ms 的即时启动功能。

CrossLink 器件的一个示例是 LIF-MD6000-6JMG80I,具有 5,936 个逻辑单元和 37 个 I/O,总 RAM 位数为 184,320。在着手开始嵌入式视觉设计时,设计人员可借助 LF-EVDK1-EVN 嵌入式视觉开发套件,将基于 CrossLink 的 MIPI 输入与 ECP5 FPGA 处理整合,用以进行嵌入式视觉设计的原型开发(图 4)。