具有 I/O 和电源管理功能:MachXO FPGA

MachXO FPGA 具有数百个 I/O,对需要 GPIO 扩展、接口桥接和上电管理功能的各种应用而言,可谓绝佳选择。系列中的最新产品旨在符合 NIST 标准,另增安全功能以确保系统硬件和固件的安全性。

MachXO FPGA 具有一组功能强大的 GPIO,包括“热插拔”等功能,因而无论电源轨状态如何,都可向 I/O 施加电压。此外,虽然多数 FPGA 输入默认为上拉状态,但 MachXO 输入默认为下拉状态,因此非常适合控制功能应用。MachXO FPGA 具有不足 10 ms 的即时启动功能,可作为“先启后停”控制器件的理想解决方案,在系统上电和断电期间用于对其他元器件进行管理和排序。

MachXO 器件的配置数据存储在闪存中。这类器件也包含基于 SRAM 的配置单元。器件上电后,存储于闪存的配置数据将以并行传输方式自动复制到基于 SRAM 的配置单元中。此外,器件运行时,可将新配置加载至闪存中,之后可选择在适当的时候将新配置复制到 SRAM 单元中。

MachXO 器件的一个典型示例是 LCMXO3LF-9400C-6BG256C,具有 9,400 个逻辑单元和 206 个 I/O,总 RAM 位数为 442,368。代表性开发板是 LCMXO3LF-6900C-S-EVN MachXO3 入门套件(MachX03L 版本)。

套件板具有 SPI 闪存,可用于评估外部启动或双重启动功能。评估 MIPI DSI 和 CSI2 I/O 时,建议使用 LCMXO3L-DSI-EVN MachXO3L DSI 分线板;评估高速差分 I/O 时,建议使用 LCMXO3L-SMA-EVN MachXO3L SMA 分线板。

Lattice Semiconductor 的 FPGA 设计和开发

伴随 FPGA 发展的最常见技术之一是语言驱动设计 (LDD)。这涉及使用 Verilog 或 VHDL 等硬件描述语言 (HDL),在抽象级别(即寄存器传送级 (RTL))上捕获设计意图。通过逻辑仿真进行验证之后,该表达式将连同目标 FPGA 类型、引脚分配和时序约束(例如最大输入到输出延迟)等其他信息一并传输至合成引擎。合成引擎输出的配置文件可以直接加载至 FPGA 中,或者对基于 SRAM 的 FPGA 而言,可加载至外部存储器件中。

Lattice Diamond 属于这类工具,可提供完整的基于 GUI 的 FPGA 设计和验证环境,适用于 CrossLink、MachXO 和 ECP 器件。

与 Lattice Diamond 一样,Lattice Radiant 也可提供完整的基于 GUI 的 FPGA 设计和验证环境,但后者主要针对 iCE FPGA 和未来架构。

Lattice Radiant 功能众多:

行业标准 IEEE 1735 知识产权 (IP) 加密和 Synopsys 设计约束 (SDC),实现最佳互操作性

集成的工具组环境,简化设计导航和调试功能

全新的 Process Toolbar 支持简单的“一键式”设计执行功能

完整的物理到逻辑闭环设计流程,实现交叉探索

IP 数据打包功能,使开发人员和第三方 IP 提供商能够以适合分发的形式打包经加密的 IP 数据包

LatticeMico 系统开发工具

Lattice 推出了两款软处理器内核——LatticeMico8 和 LatticeMico32,两者均可应用于 FPGA 的可编程结构。

LatticeMico8 是一款 8 位微控制器,针对 MachXO2 可编程逻辑器件 (PLD) 系列进行了优化和全面测试。此外,该器件也可用于其他 FPGA 系列的参考设计。微控制器内核结合了完整的 18 位宽指令集与 32 个通用寄存器,在保留丰富功能的同时,最大限度地减少消耗的器件资源——最小配置中 LUT 少于 200 个。

LatticeMico32 是一款 32 位哈佛架构 RISC 微处理器。LatticeMico32 结合了 32 位宽指令集与 32 个通用寄存器,因而性能和灵活性适合各种市场应用。采用 RISC 架构,在确保性能满足各种应用所需的同时,使内核消耗的器件资源最少。为了加速微处理器系统的开发,可将 LatticeMico32 与几种兼容 WISHBONE 控制器的可选外设元器件集成。

LatticeMico 系统开发工具具有图形用户界面,使用户可对 LatticeMico 处理器内核和外设进行拖放式操作,将其连接至总线,并为各元器件定义各种参数,例如在处理器地址空间中的位置。系统定义完成后,该工具即可自动生成相应的 RTL 以进行仿真和合成。此外,该系统提供的工具使用户能够生成软件,用以在处理器内核上运行。

机器学习工具:Lattice sensAI 堆栈和神经网络编译器

目前,机器学习 (ML) 和人工智能 (AI) 应用广泛部署于各种嵌入式系统和整个物联网 (IoT),包括工业物联网 (IIoT)。

Lattice sensAI 堆栈包含评估、开发和部署基于 FPGA 的 ML/AI 解决方案所需的一切功能,包括模块化硬件平台、示例演示、参考设计、神经网络 IP 内核,软件开发工具和定制设计服务。在消费类和工业物联网应用中,开发人员可借助该堆栈实现灵活的机器学习推断引擎,加快上市时间。

Lattice 卷积神经网络 (CNN) 加速器 IP 内核是用于深度神经网络 (DNN) 的计算引擎。该引擎针对卷积神经网络进行了优化,因此可用于分类、对象检测和跟踪等基于视觉的应用。CNN IP 内核本身可执行所需的计算,因此无需额外添加处理器。

同时,借助 Lattice 神经网络编译器,设计人员可使用 TensorFlow、Caffe 和 Keras 等通用开发框架下创建的神经网络,并将其编译以在 Lattice CNN 和紧凑型 CNN 加速器 IP 内核中实施。

小结

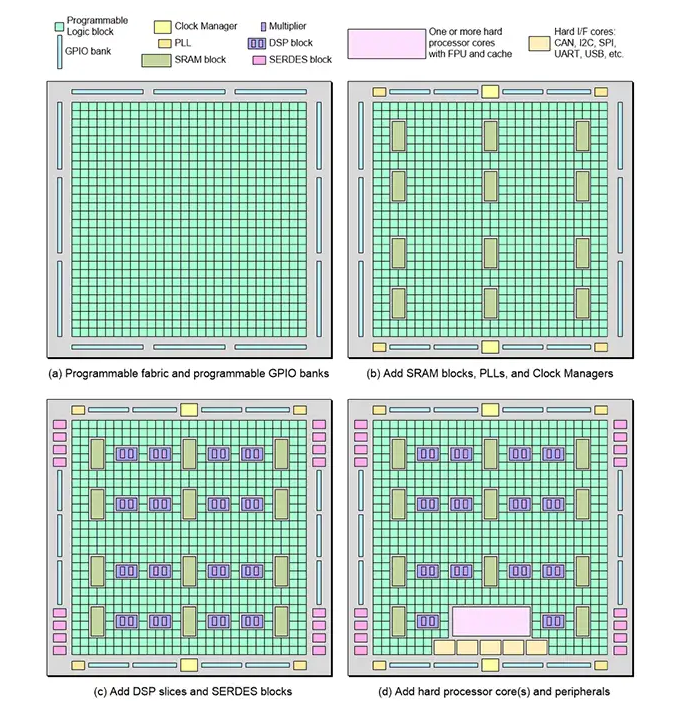

最佳设计解决方案常常是由处理器与 FPGA 的组合提供,或由 FPGA 单独提供,或以硬处理器内核作为部分结构的 FPGA 提供。作为一项技术,FPGA 多年来发展迅速,如今已经能够满足灵活性、处理速度、功耗等多方面的设计需求,非常适合智能接口、机器视觉和 AI 等众多应用。

如上所述,Lattice Semiconductor 的 FPGA 产品范围覆盖低中端,专注于低功耗器件,应用遍及通信、计算、工业、汽车和消费类等迅速增长的市场,以此解决从边缘到云的网络问题。此外,Lattice 还推出了若干设计和验证工具套件,适用于基于语言的设计、基于图形处理器的设计以及专注于机器学习和人工智能应用的设计等各种设计流程。