如果你学习可编程逻辑设计,一定接触过CPLD和FPGA,那它们有什么不同呢?就像你看到标题一样到底是要说CPLD还是FPGA,其实这并不是重点。 也许你能得到这样的答案,CPLD是基于宏单元,采用EEPROM技术,无需外部配置器件,上电瞬时接通;而FPGA基于查找表结构,采用SRAM技术, 上电需要外部重新配置,但是逻辑资源较CPLD更多;总的来说CPLD适合组合逻辑的设计而FPGA更适合比较复杂的时序逻辑设计。这些都没有错,不过随着技术进步以及芯片集成度的提高,CPLD与FPGA的分别已经越来越模糊。

CPLD优点固然突出,不过受制于宏单元的结构限制,逻辑单元的密度达到上限。如何突破传统CPLD的架构,Altera早在其MAX II系列器件就进行了革命性的设计。如下图所示MAX II器件采用了和FPGA一样的高密度逻辑单元设计,同时片上集成了非易失性FLASH存储块用作配置模块,这样既能提高芯片的逻辑单元密度,又能够实现像CPLD器件一样的上电瞬时接通能力。

MAX II器件平面图

今年Altera又推出了其最新的MAX 10系列(MAX 10数据手册)可编程器件,可以说是CPLD的又一次革命,已经完全模糊了CPLD和FPGA的界限。MAX 10不仅继承了之前MAX系列器件的特性,而且逻辑资源密度大幅提升,最高有50K逻辑单元(LE),完全不逊于一些低端的FPGA器件。更为重要的是MAX 10还包括了全功能FPGA特性,如嵌入式处理器软核、DSP模块、DDR3存储控制器等等。可以说MAX 10其实是一种非易失性的FPGA。

MAX 10体系结构

通过上面的体系结构图可以了解MAX 10的新特性:

- 双配置闪存: 一个芯片上可以存储两个镜像,在镜像间动态切换

- 模拟模块: 集成ADC、电源管理以及温度传感器

- 瞬时接通: 配置时间毫秒级

- Nios II 软核嵌入式处理器:支持 Altera 软核 Nios II 嵌入式处理器的集成,提供了单芯片、完全可配置的瞬时接通处理器子系统。

- DSP 模块:第一款具有 DSP 的 非易失性FPGA

- DDR3 外部存储器接口:MAX 10通过软核IP存储控制器支持 DDR3 SDRAM 和 LPDDR2 接口,适合视频、数据通路和嵌入式应用。

- 用户闪存:具有 736 KB 用户闪存代码存储功能,支持Nios II 嵌入式应用。用户闪存容量取决于配置选择。

目前MAX 10系列已经有7个产品线,从10M02到10M50,逻辑单元从2000到50000,如下图所示。

MAX 10 产品线

CPLD一般具有更低单位成本的IO,因此常用于组合逻辑以及开关选择的设计,从上表可以看到最大MAX 10器件逻辑资源达到50000个,用户IO也达到500。同时MAX 10 FPGA非常适合做高性价比的单芯片方案,因此MAX 10适合非常多的市场领域和应用,例如工业上既可作I/O模组也可作视频监控。MAX 10系列同时提供商业级、工业级以及汽车级温度范围的芯片,因此在工业、汽车、消费类领域MAX 10都可以大显身手。

评估套件EK-10M08E144ES/P

当然评估以及设计FPGA电路一定需要开发板,目前已经推出了4种MAX 10开发套件,爱板网这次收到的是来自Altera的MAX 10 FPGA评估套件EK-10M08E144ES/P,下面来看看这款高性价比的入门评估套件。(下一页)

MAX 10 FPGA评估套件

Altera的MAX 10 FPGA评估套件是一款低成本的入门套件,目前售价不超过50美元。评估套件采用了很简单塑料封装,一块开发板以及一根mini-B USB电缆,比较特别是包装里还附赠了4个开发板的塑料垫脚。

评估板、USB线、塑料垫脚

MAX 10 FPGA评估套件的结构很简单,除了一些按键、开关和LED等外设之外都是各种扩展接口,

MAX 10 FPGA评估套件方框图

评估套件引出了80个GPIO供用户使用,除此之外还有Arduino R3的标准接口,甚至预留了一小块“原型区”洞洞板,因此MAX 10 FPGA评估套件非常适合折腾。做原型设计或者DIY学习,使用可以说非常灵活。

MAX 10 FPGA评估套件正面

MAX 10 FPGA评估套件背面

MAX 10评估套件EK-10M08E144ES/P的主要特性包括:

- 核心器件MAX 10 FPGA(10M08SAE144C8GES,单电源供电,144引脚)

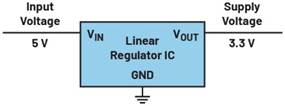

- Enpirion EP5388QI (EP5388QI数据手册)负载点 PowerSoC:800 mA、DC-DC 降压转换、带有集成电感

- 10pin JTAG

- 50 MHz晶振

- 开关、按钮、跳接器和状态 LED

- Arduino R3版兼容接口

- 80pin GPIO扩展接口

- mini-B USB接口

- 预留电位计布局

另外需要说明的是开发板的mini-B USB接口仅仅是作为电源供电接口,而且板上的DC-DC转换电源芯片的最大输出电流为800mA。开发板上只是提供了JTAG编程接口,支持Altera的USB Blaster和EthernetBlaster下载电缆,如果你手上没有Altera的编程下载电缆的话需要额外购置才能搭建开发环境了。

下面来看看开发板上的核心FPGA器件10M08SAE144C8GES,从前面的MAX 10产品列表可以知道MAX 10根据不同的逻辑资源和功能分为7个产品系列,每个产品系列里又根据封装、速度、温度等级划分,如下所示:

MAX 10器件标识定义

这样我们可以了解开发板上的芯片10M08SAE144C8GES的一些大体特点,例如8000逻辑单元、单电源、144脚QFP封装、商业温度等级、速度等级8、工程样片等等。

10M08SAE144C8GES器件QFP封装

10M08SAE144C8GES的主要特点:

- 采用了TSMC的55nm嵌入式flash制程工艺

- 144pin QFP封装,22mm x 22mm大小,最大用户IO数101个

- 8000逻辑单元(LE),支持内部存储器模块、乘法器、PLL及用户闪存

- 内部双启动自配置Flash,支持JTAG

- 支持嵌入式硬核IP如外部存储器控制、1路12位ADC

- 单电源供电,只需一路3V或3.3V电源

要了解详细部分可以查阅MAX 10器件的文档,接下来准备上电试用下评估套件。(下一页)

开发环境

使用可编程器件开发的都知道FPGA的EDA工具的重要性,熟悉使用EDA工具也是不小的挑战。MAX 10是Altera新推出的器件,支持的Quartus II软件版本是14.0.2以上,目前最新的版本是14.1。没办法首先要到Altera官网去下载Quartus II。

Quartus II软件下载页

Quartus II14.1的文件很大,分为主文件、Modelsim文件和器件支持文件,可以按需求下载。这里要提醒一下Quartus II14.0之后的版本只能运行在64位的系统下。

MAX 10 FPGA评估套件只提供了JTAG接口,因此要搭建开发环境必须有Altera的下载电缆,例如USB Blaster,

USB Blaster下载电缆

安装Quartus II时会提示安装USB Blaster的驱动,这样才算准备好了整个开发环境。

上电工作

准备工作完成以后,我们上电看看MAX 10的工作情况。评估套件上的预置的程序是点亮用户LED,每隔0.5S闪烁。连接好USB先后,MAX 10瞬时通电工作,相比普通的FPGA需要时间配置程序确实快很多。MAX 10的内部Flash配置时间只需要10ms,根本感觉不到。

评估套件内置程序

现在可以在MAX 10上开始自己的FPGA设计了。Altera的设计商店(Design Store)提供了MAX 10评估套件一系列例程,对于新手来说是必不可少。

MAX 10 FPGA评估套件设计商店

在设计商店下载的工程文件是.par的打包文件,可以通过命令行模式解压,具体请看网页说明。而Quartus II14.1版本增加了直接导入文件模板的功能,导入例程更加方便。在File菜单下选New Project Wizard新建工程,

导入例程

这里可以直接导入工程模板,例如我们导入Baseline Design例程,这个程序top文件只有引脚定义,不完成任何功能。不过这个程序非常有用,因为它已经定义好了MAX 10评估套件上的MAX 10芯片的引脚,我们之后开始任何设计都可以基于这个例程,这样不需要重新设定引脚。在Assignment下的Assignment Editor下可以看到每个引脚的定义,同时我们也可以手动修改。当然你也可以通过Pin planner看到引脚的图形化布局。

评估套件MAX 10芯片引脚定义

(下一页)

双启动Flash配置

MAX系列CPLD在MAX II之后最重要的变化就是内置了Flash配置模块,从而实现了CPLD的瞬时上电工作。而MAX 10更是引入了一种很有意思新技术内置双启动模式,可以在一个芯片内实现双配置,通过芯片的Boot_sel引脚实现两种配置的切换。

配置示意图

单芯片双配置的方案使你的设计更加灵活,在某些需要额外Flash芯片配置场合更加节省成本。MAX 10系列中除了10M02之外都能够支持双启动模式。

MAX 10芯片中的Flash可以分为配置模块(CFM)和用户模块(UFM),其中CFM0模块是专门用于配置,而CFM1模块在单配置模式下可以作为UFM。例如10M08芯片中Flash大小一共为2496kb,其中CFM0占1120Kb,CFM1占1120Kb,这样在双启动模式下用户可用Flash只有256Kb,而在单配置模式下用户可用Flash最大可达到1376Kb。MAX 10芯片的内部配置有5种模式:

- 双压缩映像(256Kb UFM)

- 单压缩映像(1376Kb UFM)

- 存储器初始化的单压缩映像(256Kb UFM)

- 单未压缩映像(912Kb UFM)

- 存储器初始化的单未压缩映像(256Kb UFM)

在Assignment菜单的Device下的Device and Pin Option可以设置配置模式

设定工程配置模式

IP核在如今FPGA设计越来越不可少,双配置功能也需要使用到Altera Dual Configration IP,实现双配置需要分3步:

- 在工程中添加双启动IP

- 配置模式选择内部双配置模式

- 利用Convert Program file将2个工程的sof文件转化成pof文件

Altera的设计商店提供了一个Dualboot例程,这是一个简单的双启动程序,当Boot_sel=0时(开关SW3中的开关6)交替点亮LED1和LED2,而Boot_sel=1时交替点亮LED3和LED4。Dualboot例程的两个工程文件是集成在了一个Project里,

Dual_boot例程

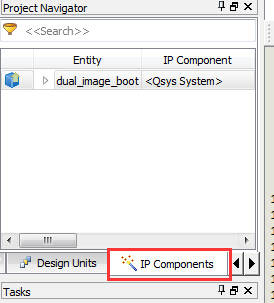

例程已经在程序中例化好了双配置IP——dual_image_boot,打开Qsys可以看到IP的连线,

Dual_boot IP

编译image0和image1两个工程后会生成sof文件,打开File下的Convert Program File可以转化最后的pof文件

生成pof编程文件

最后可以下载程序到MAX 10的内部Flash。

编译MAX 10界面

下载完成后重新上电

SW3的第6个开关向上,交替点亮LED1和LED2

SW3的第6个开关向下,交替点亮LED3和LED4

可以看到改变SW3的第6个开关就可以改变MAX 10的配置程序。总的来说增加双配置功能也很方便,

- 首先用Qsys工具生成一个Dual boot的IP,这里注意时钟的频率和连线;

- 然后将该IP例化到我们的程序中,可以参考例程;

- 之后修改工程的配置模式;

- 最后转化为能够烧录Flash的pof文件。

小结

介绍了Altera最新推出的MAX 10具有非易失性能的可编程器件,既具有FPGA的大容量又能够实现CPLD的瞬时上电工作。体验了Altera的MAX 10 FPGA评估套件的性能,尤其是双启动特性。MAX 10 FPGA评估套件可扩展性非常强,唯一不方便是需要额外购置Altera的下载电缆。关于评估套件的一些其他性能体验将陆续更新,敬请期待。

相关阅读:

手把手教你用MAX 10入门FPGA

参考资料

- Altera MAX 10 FPGA官网简介

- Altera MAX 10 FPGA视频教程

- MAX 10 FPGA 评估套件

- MAX 10 FPGA 评估套件设计商店例程

- Quartus II软件下载

原创申明:本文为爱板网原创,谢绝转载!

如果你学习可编程逻辑设计,一定接触过CPLD和FPGA,那它们有什么不同呢?就像你看到标题一样到底是要说CPLD还是FPGA,其实这并不是重点。 也许你能得到这样的答案,CPLD是基于宏单元,采用EEPROM技术,无需外部配置器件,上电瞬时接通;而FPGA基于查找表结构,采用SRAM技术, 上电需要外部重新配置,但是逻辑资源较CPLD更多;总的来说CPLD适合组合逻辑的设计而FPGA更适合比较复杂的时序逻辑设计。这些都没有错,不过随着技术进步以及芯片集成度的提高,CPLD与FPGA的分别已经越来越模糊。

CPLD优点固然突出,不过受制于宏单元的结构限制,逻辑单元的密度达到上限。如何突破传统CPLD的架构,Altera早在其MAX II系列器件就进行了革命性的设计。如下图所示MAX II器件采用了和FPGA一样的高密度逻辑单元设计,同时片上集成了非易失性FLASH存储块用作配置模块,这样既能提高芯片的逻辑单元密度,又能够实现像CPLD器件一样的上电瞬时接通能力。

MAX II器件平面图

今年Altera又推出了其最新的MAX 10系列(MAX 10数据手册)可编程器件,可以说是CPLD的又一次革命,已经完全模糊了CPLD和FPGA的界限。MAX 10不仅继承了之前MAX系列器件的特性,而且逻辑资源密度大幅提升,最高有50K逻辑单元(LE),完全不逊于一些低端的FPGA器件。更为重要的是MAX 10还包括了全功能FPGA特性,如嵌入式处理器软核、DSP模块、DDR3存储控制器等等。可以说MAX 10其实是一种非易失性的FPGA。

MAX 10体系结构

通过上面的体系结构图可以了解MAX 10的新特性:

- 双配置闪存: 一个芯片上可以存储两个镜像,在镜像间动态切换

- 模拟模块: 集成ADC、电源管理以及温度传感器

- 瞬时接通: 配置时间毫秒级

- Nios II 软核嵌入式处理器:支持 Altera 软核 Nios II 嵌入式处理器的集成,提供了单芯片、完全可配置的瞬时接通处理器子系统。

- DSP 模块:第一款具有 DSP 的 非易失性FPGA

- DDR3 外部存储器接口:MAX 10通过软核IP存储控制器支持 DDR3 SDRAM 和 LPDDR2 接口,适合视频、数据通路和嵌入式应用。

- 用户闪存:具有 736 KB 用户闪存代码存储功能,支持Nios II 嵌入式应用。用户闪存容量取决于配置选择。

目前MAX 10系列已经有7个产品线,从10M02到10M50,逻辑单元从2000到50000,如下图所示。

MAX 10 产品线

CPLD一般具有更低单位成本的IO,因此常用于组合逻辑以及开关选择的设计,从上表可以看到最大MAX 10器件逻辑资源达到50000个,用户IO也达到500。同时MAX 10 FPGA非常适合做高性价比的单芯片方案,因此MAX 10适合非常多的市场领域和应用,例如工业上既可作I/O模组也可作视频监控。MAX 10系列同时提供商业级、工业级以及汽车级温度范围的芯片,因此在工业、汽车、消费类领域MAX 10都可以大显身手。

评估套件EK-10M08E144ES/P

当然评估以及设计FPGA电路一定需要开发板,目前已经推出了4种MAX 10开发套件,爱板网这次收到的是来自Altera的MAX 10 FPGA评估套件EK-10M08E144ES/P,下面来看看这款高性价比的入门评估套件。(下一页)

MAX 10 FPGA评估套件