NXP公司的S32R274是基于32位Power Architecture的用于汽车和工业雷达的MCU,安全核采用e200Z4 32位CPU,计算核采用e200Z7 32位CPU,集成了带ECC的2MB代码闪存(FMC闪存)和带ECC的1.5MB SRAM,雷达接口包括MIPI-CSI2 (4数据链),ΣΔ-ADC (4x 12位10 MSps)和DAC (10 MSps),其它接口包括Zipwire, 2x SAR-ADC, 2x SPI, 2x I2C, 3x FlexCAN (incl. 2x CAN-FD), Flexray™, LINFlexD和以太网,工作温度-40 到150˚ CAEC-Q100 Grade 1.本文介绍了S32R274主要特性,框图和系列产品性能比较表,以及评估板S32R274EVB主板和子板主要特性以及电路图.

The S32R27 is a 32-bit Power Architecture based microcontroller for automoTIve and industrial radar applicaTIons. It offers >4x leap in performance per power vs the previous MPC577X products, and increases the level of integraTIon available to designers of next generaTIon automotive radar modules. Designed to address advanced radar signal processing capabilities and merge it with microcontroller capabilities for generic software tasks and car bus interfacing. It meets the high performance computation demands required by modern beam-forming fast chirp modulation radar systems by offering unique signal processing acceleration together with powerful multi-core architecture.

S32R274主要特性:

• On-chip modules available within the device includethe following features:

• Safety core: Power Architecture? e200Z4 32-bit CPUwith checker core

• Dual issue computation cores: Power Architecture®e200Z7 32-bit CPU

• 2 MB on-chip code flash (FMC flash) with ECC

• 1.5 MB on-chip SRAM with ECC

• RADAR processing

– Signal Processing Toolbox (SPT) for RADAR signalprocessing acceleration

– Cross Timing Engine (CTE) for precise timinggeneration and triggering

– Waveform generation module (WGM) for chirpramp generation

– 4x 12-bit ΣΔ-ADC with 10 MSps

– One DAC with 10 MSps

– MIPICSI2 interface to connect external ADCs

• Memory Protection

– Each core memory protection unit provides 24entries

– Data and instruction bus system memory protectionunit (SMPU) with 16 region descriptors each

– Register protection

• Clock Generation

– 40 MHz external crystal (XOSC)

– 16 MHz Internal oscillator (IRCOSC)

– Dual system PLL with one frequency modulatedphase-locked loop (FMPLL)

– Low-jitter PLL to ΣΔ-ADC and DAC clockgeneration

• Functional Safety

– Enables up to ASIL-D applications

– FCCU for fault collection and fault handling

– MEMU for memory error management

– Safe eDMA controller

– Self-Test Control Unit (STCU2)

– Error Injection Module (EIM)

– On-chip voltage monitoring

– Clock Monitor Unit (CMU)

• Security

– Cryptographic Security Engine (CSE2)

– Supports censorship and life-cycle management

• Timers

– Two Periodic Interval Timers (PIT) with 32-bitcounter resolution

– Three System Timer Module (STM)

– Three Software Watchdog Timers (SWT)

– Two eTimer modules with 6 channels each

– One FlexPWM module for 12 PWM signals

• Communication Interfaces

– Two Serial Peripheral interface (SPI) modules

– One LINFlexD module

– Two inter-IC communication interface (I2C)modules

– One dual-channel FlexRay module with 128message buffers

– Three FlexCAN modules with configurable buffers -CAN FD optionally supported on 2 FlexCANmodules

– One ENET MAC supporting MII/RMII/RGMIIinterface

– ZipWire high-speed serial communication

• Debug Functionality

– 4-pin JTAG interface and Nexus/Aurora interfacefor serial high-speed tracing

– e200Z7 core and e200Z4 core: Nexus developmentinterface (NDI) per IEEE-ISTO 5001-2012 Class 3+

• Two analog-to-digital converters (SAR ADC)

– Each ADC supports up to 16 input channels

– Cross Trigger Unit (CTU)

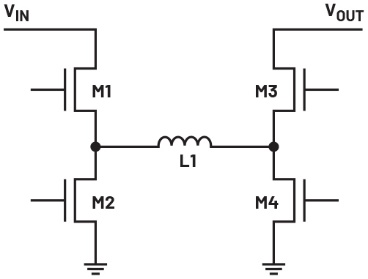

• On-chip voltage DC/DC regulator for core clock(VREG)

• Two Temperature Sensors (TSENS)

The following table provides a comparison of two devices S32R274 and MPC5775K .

This information is intended to provide an understanding of the range of functionality offered by this family. For full details of all of the family derivatives please contact your marketing representative.

S32R274系列产品比较表:

图1.S32R274框图

技术专区

- TIDA-01421用于无传感器位置测量的脉冲计数器参考设计

- 传特斯拉明年11月生产ModelY_与Model3同一平台

- TLE9842-2QX主要特性_PCB设计图

- CMU机器人研究所_无人驾驶上路测试牌照Gatik.AI

- DRV10983-Q1主要特性_功能框图